Interface IP Cores for TSMC

Welcome to the ultimate

Interface IP Cores

for

TSMC

hub! Explore our vast directory of

Interface IP Cores

for

TSMC

All offers in

Interface IP Cores

for

TSMC

Filter

Compare

60

Interface IP Cores

for

TSMC

from

4

vendors

(1

-

10)

Filter:

- 6nm

-

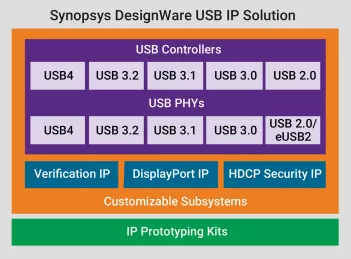

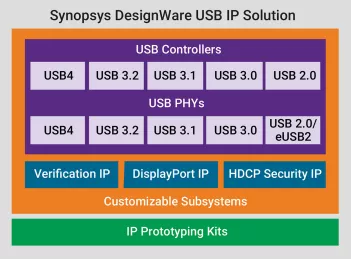

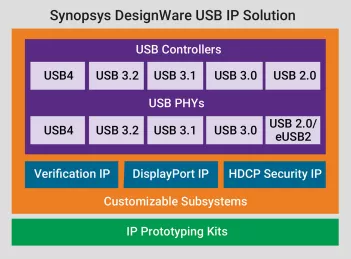

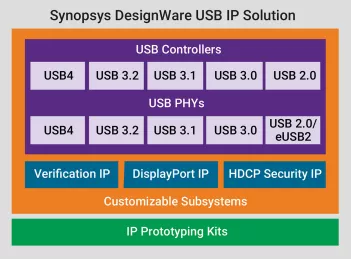

USB4 PHY - TSMC N6 1.8V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

-

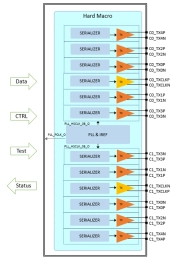

LVDS / sub-LVDS / DPHY TX - TSMC 6FFC

- The LVDS/Sub-LVDS/DPHY Combo TX converts parallel RGB data and 7/8/10 bits of CMOS parallel data into serial data streams.

- A phase-locked clock is transmitted in parallel with the data streams over a dedicated high-speed link.

- The polarity of differential signals for each data lane can be controlled.

-

USB 2.0 femtoPHY -TSMC N6 18 x1, OTG, North/South (vertical) poly orientation

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

USB-C 3.1 SS/SSP PHY, Type-C - TSMC 6FF x1, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC 6FF x1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

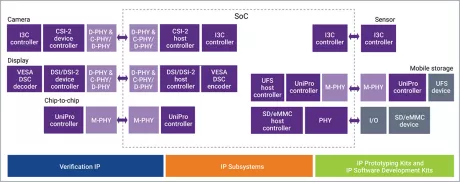

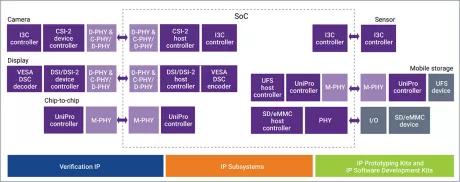

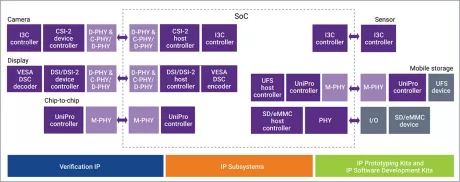

MIPI M-PHY G5 Type 1 2Tx2Rx - TSMC N6 1.8V, North/South Poly Orientation

- Compliant with MIPI M-PHY v5.0 specification

- Supports MIPI UniPro, JEDEC UFS protocols

- Supports High-Speed (HS) Gear1,

- Gear2, Gear3, Gear4 and Gear5 A/B modes

- Supports M-PHY Type-I

-

MIPI M-PHY G4 Type 1 2TX2RX - TSMC 6FF 1.8V, North/South Poly Orientation

- Compliant with MIPI M-PHY v5.0 specification

- Supports MIPI UniPro, JEDEC UFS protocols

- Supports High-Speed (HS) Gear1,

- Gear2, Gear3, Gear4 and Gear5 A/B modes

- Supports M-PHY Type-I

-

MIPI D-PHY Tx 4 Lanes - TSMC6ff18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Tx 2 Lanes - TSMC6ff18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 4 Lanes - TSMC6ff18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes