PLL IP for TSMC

Welcome to the ultimate

PLL IP

for

TSMC

hub! Explore our vast directory of

PLL IP

for

TSMC

All offers in

PLL IP

for

TSMC

Filter

Compare

39

PLL IP

for

TSMC

from

5

vendors

(1

-

10)

Filter:

- 3nm

-

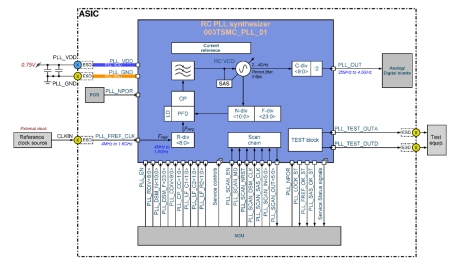

25MHz to 4.0GHz Fractional-N RC PLL Synthesizer on TSMC 3nm N3P

- Fractional-N Phase locked loop frequency synthesizer is intended for ASIC clock generation.

- The Fractional-N PLL loop with 2GHz-4GHz VCO has high phase noise performance and ultra-fine frequency tuning step.

- VCO Sub-band auto select (SAS) system allows to find automatically appropriate sub-band for VCO on locked PLL.

-

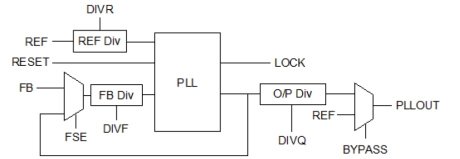

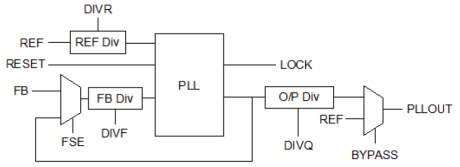

Core Powered Wide Range Programmable Integer PLL on TSMC CLN3P-CLN3X

- Entirely core voltage powered, needs no analog supply voltage

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

-

Core Powered Wide Range Programmable Integer PLL on TSMC CLN3E

- Entirely core voltage powered, needs no analog supply voltage

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

-

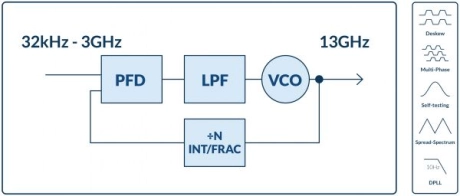

General-purpose & Specialized Ring PLLs + RTL-based Solutions

- Wide functional range allows all frequencies in a system to be synthesized with one PLL macro

- Input & output frequency ranges greater than 1000:1

-

Wide Range Programmable Integer PLL on TSMC CLN3P-CLN3X

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Small area footprint

-

Wide Range Programmable Integer PLL on TSMC CLN3E

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Small area footprint

-

PCIe Gen4/5/6 Class Low Jitter LC PLL on TSMC CLN3P-CLN3X

- High performance design emphasis for meeting low jitter requirements in PCIe Gen4 & Gen5 applications

- Implemented with Analog Bits’ proprietary LC architecture

- Low power consumption

- Spread Spectrum Clock Generation (SSCG) and tracking capability

-

PCIe Gen4/5/6 Class Low Jitter LC PLL on TSMC CLN3E

- High performance design emphasis for meeting low jitter requirements in PCIe Gen4 & Gen5 applications

- Implemented with Analog Bits’ proprietary LC architecture

- Low power consumption

- Spread Spectrum Clock Generation (SSCG) and tracking capability

-

High Performance 20GHz C2C PLL on TSMC CLN3P-CLN3X

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Low power consumption

-

High Performance 20GHz C2C PLL on TSMC CLN3E

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Low power consumption