Clocking IP for TSMC

Welcome to the ultimate

Clocking IP

for

TSMC

hub! Explore our vast directory of

Clocking IP

for

TSMC

All offers in

Clocking IP

for

TSMC

Filter

Compare

122

Clocking IP

for

TSMC

from

8

vendors

(1

-

10)

Filter:

- 16nm

-

Crystal Oscillators

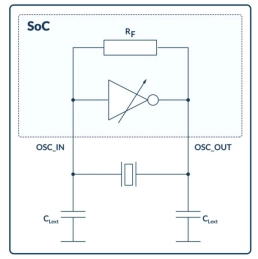

- The crystal oscillator macros are available in a wide range of industry-standard quartz crystals and MEMS resonators operating in the fundamental mode in the 32 kHz to 80 MHz range.

- These oscillators, which are both power and area efficient, have a programmable transconductance to allow users to find the optimal balance between jitter and power consumption.

-

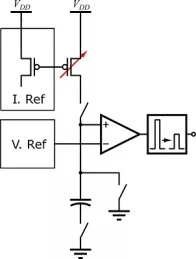

Free running oscillators

- Compact and low power

- No external components

- Baseline CMOS logic process masks only

- Excellent frequency precision over PVT after trimming

-

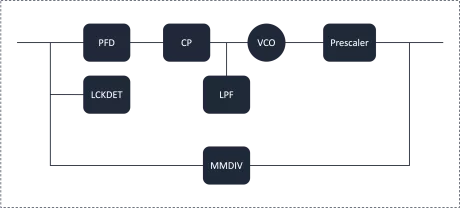

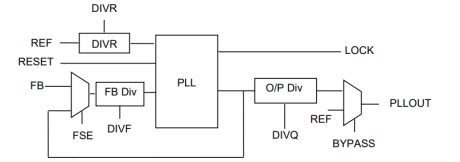

Wide Range Programmable Integer PLL on TSMC CLN16FFC

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Fully integrated inside customer-specified IO ring

-

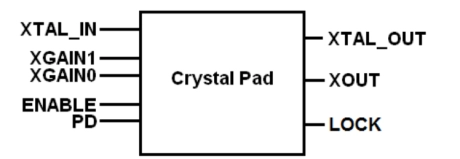

20-40MHz Crystal Oscillator on TSMC CLN16FFC

- Crystal Oscillator pad macro that supports industry standard crystals in the 20-40MHz range

- Uses standard CMOS transistors

- Crystal Oscillation Mode: Fundamental

- Power down option for IDDQ testing

-

LVDS 160MHz 8-Lane PHY TX IP on TSMC 16FFC

- The CL12491M8TIP160 transmitter converts parallel RGB data and 4bits of HYNC,VSYNC,DE and Control) of CMOS parallel data into serial LVDS data streams.

- A phase-locked clock is transmitted in parallel with the data streams over a dedicated LVDS link.

- The polarity of differential signals for each data lane can be controlled.

-

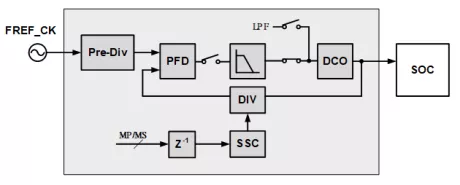

3GHz, low jitter fractional-N, Digital PLL, TSMC 16FFC, N/S orientation

- Pure core voltage design

- Compact IP size (< 0.013mm²) and low power consumption (1.1mW @ 3GHz)

- Compatible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter (< ±15%/V)

-

4.8GHz low jitter fractional-N, Digital PLL, TSMC 16FFC, N/S orientation

- Pure core voltage design

- Compact IP size (< 0.013mm²) and low power consumption (1.1mW @ 3GHz)

- Compatible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter (< ±15%/V)

-

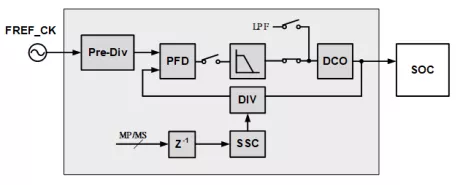

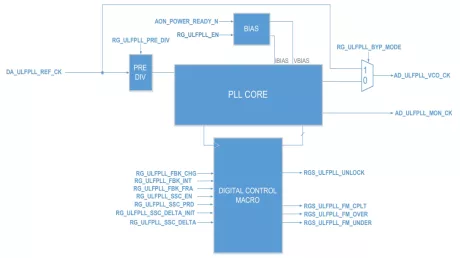

Ultra-Low Power Fractional PLL IP in in TSMC (12/16nm FFC, 22nm ULP/ULL, 28nm HPC+)

- Supports wide input frequency range: 10MHz to 240MHz

- Supports 3:1 output frequency range allows optimization for power and jitter performance

- 24-bit fractional accuracy

- Supports Spread Spectrum Clocking

-

Low Power Fractional PLL IP in TSMC(12/16nm FFC, 22nm ULP/ULL, 28nm HPC+)

- Compact IP size ( smaller than 0.01mm²) and low power consumption ( < 2.7mW @ 3.5GHz )

- Compactible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter ( < +-15ps )

- Support 24-bit fractional accuracy

-

14GHz Integer-N High-Speed PLL

- Type II hybrid Integer-N LC-PLL

- Quadrature clocks at 14GHz and 7GHz

- Fast locking