Analog IP for Tower

Welcome to the ultimate

Analog IP

for

Tower

hub! Explore our vast directory of

Analog IP

for

Tower

All offers in

Analog IP

for

Tower

Filter

Compare

33

Analog IP

for

Tower

from

8

vendors

(1

-

10)

-

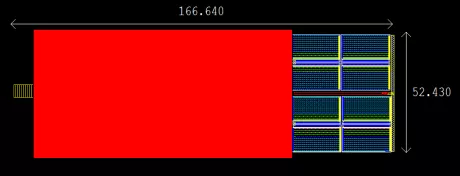

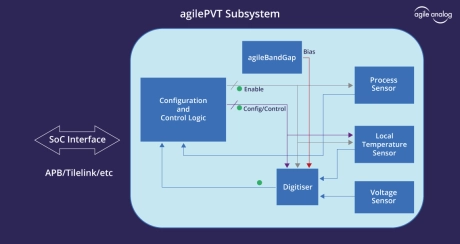

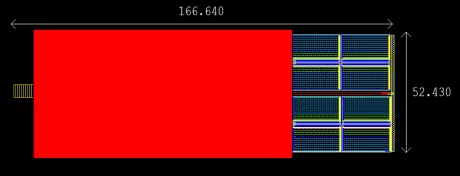

PVT Sensor Subsystem

- Start-up time: Typ 20us

- Current consumption: Max 25uA

- Industry standard digital interface

- Fully integrated macro

- Standard AMBA APB interface

-

CC-100IP-RF Analog and RF Sensitivity Enhancement IP

- Enhances the Sensitivity of Analog and RF Frontend Receivers

- Enhances the PSRR od Analog and RF Frontend Receivers

- Occupies the same on chip area as standard DCAPs with at least a 600X effective capacitance increase

- Up to a 36% Dynamic Power and RF Emissions Reduction

-

Revolutionaly Ultra Low Phase Noise RF Amplifier-LNA IP

- Revolutionary Ultra Low Phase Noise operation

- Ultra Low Power Operation

- RF front end sensitivity enhancement

-

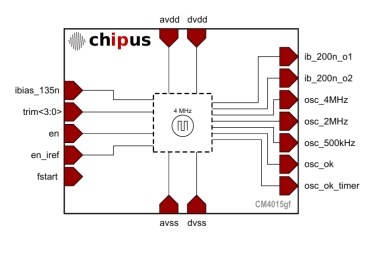

4MHz Low Power Oscillator - Low power (4.6µW), Internal Current Reference TowerJazz 0.18 um

- This macro-cell is a general purpose, low power, 4MHz internal oscillator core designed for TowerJazz TS18SL 0.18μm CMOS technology.

- Two other oscillator outputs are available: 2MHz and 500kHz.

-

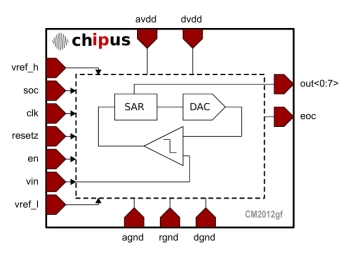

Low-Power 8-bit SAR ADC - 8 bits, 50kSPS, Low Voltage (1.8V), Low Power (20µA) TowerJazz 0.18 um

- This macro-cell is a low power, general purpose, 8-bit, 50kSPS, Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) core designed for TowerJazz 0.18μm TS18SL CMOS technology.

- The circuit has an internal sample-and-hold circuit and a power-down operation mode to save power in applications where power consumption is critical.

-

-

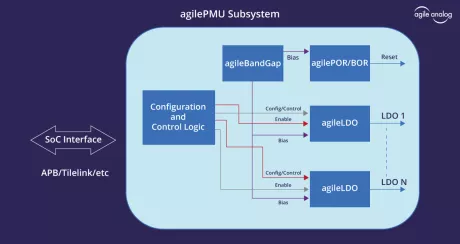

Power Management Subsystem

- The agilePMU Subsystem is an efficient and highly integrated Power Management Unit for SoCs/ASICs.

- Featuring a Power-On-Reset (POR), multiple Low Drop-Out (LDO) regulators, and an associated reference generator.

- The agilePMU Subsystem is designed to ensure low power consumption while providing optimal power management capabilities.

-

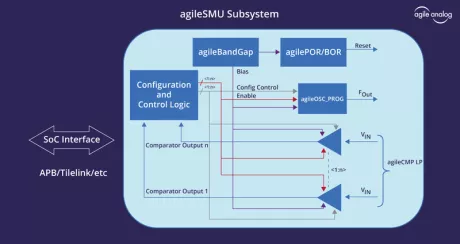

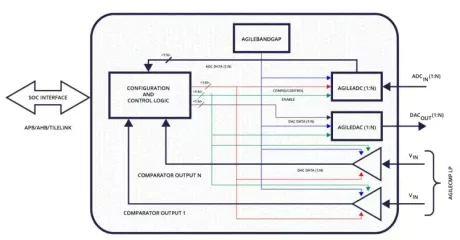

Sensor Interface Subsystem

- The agileSensorIF Subsystem is an efficient and highly integrated sensor interface for SoCs/ASICs.

- Featuring multiple Analog-to-Digital Converters (agileADC), Digital-to-Analog Converters (agileDAC), low-power programmable analog comparators (agileCMP_LP), and an associated reference generator (agileREF).

- The agileSensorIF Subsystem enables easy interaction with the analog world.

-

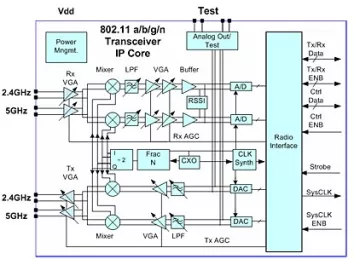

802.11 A/B/G/N Direct Conversion Transceiver

- Fully Integrated 802.11 a/b/g/n Transceiver

- High Performance

- Low Power Consumption

-

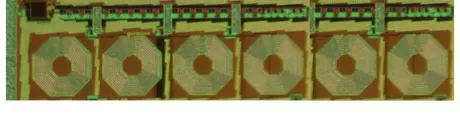

Hyper-Decoupling Capacitor with a Capacitance Multiplication, Series Inductance Nullification, Cybersecurity Enhancement and an Energy Harvesting capabilities

- Occupies the same on chip area as standard DCAPs with at least a 600X effective capacitance increase

- Up to a 36% Dynamic Power and RF Emissions Reduction

- On-Chip Cybersecurity Enhancement

- 25% Reduction in Capacitor ESL