Revolutionaly Ultra Low Phase Noise RF Amplifier-LNA IP

The CC-202IP Cell, can be cascaded to form a multistage RF amplifier/LNA/Filter.

Overview

The CC-202IP Cell, can be cascaded to form a multistage RF amplifier/LNA/Filter. The CC-202IP cell, possessing a single cell gain of 30dB with a phase noise of 1.3nV per root Hz (rms) , can be cascaded multiple times (eg.cascaded 6 times, creates a 70dB gain amplifier with the total cumulative phase noise, rising to 8nV per root Hz (rms), centered at 2.5Ghz), The CC-202IP cell gain is shown to rise from approximately 30dB centered at 200Mhz for the single gain and CML/CMOS cell to nearly 70dB centered at 2.5Ghz.

Both the single cell and the multi-stage amplifier feature outputs with signal swings ranging from high CML to CMOS signal levels. The sensitivity of the CML/CMOS cell is 28mV rms or 80mV pp, creating an output SNR of -171dBc, perfectly suitable for the almost zero noise amplification of off-chip, clock crystal or resonator fundamental or odd order signal magnitudes for clean clock ADC, DAC , Track and Hold, and ultra low noise switched capacitor applications. The sensitivity of the six stage example, 6 stage multi-stage RF amplifier, operating at 2.5Ghz is 280uV rms or 800uV pp, creating an output SNR of -161dBc making this configuration suitable for RF amplifier, LNA, and PLL applications.

Key features

- Almost Zero Phase Noise per cell ( 30dB gain with 1.3nV per root Hz (rms))

- Ultra-low Noise Figure

- Noise Circles are almost irrelevant due to the low phase noise

- Selectable 2nd Order Bandwidth Adjustability

- Harmonic or Bandwidth Selectable Output

- Differential Drive Outputs

- Cascade-able Design (any number of multiple stages depending on Gain and noise requirements)

- Cascaded for increased gain and narrower bandwidth (for 6 cascaded stages,.70dB gain with 8nV perroot Hz noise (rms))

- Ultra-Low SNR (-161dBc)

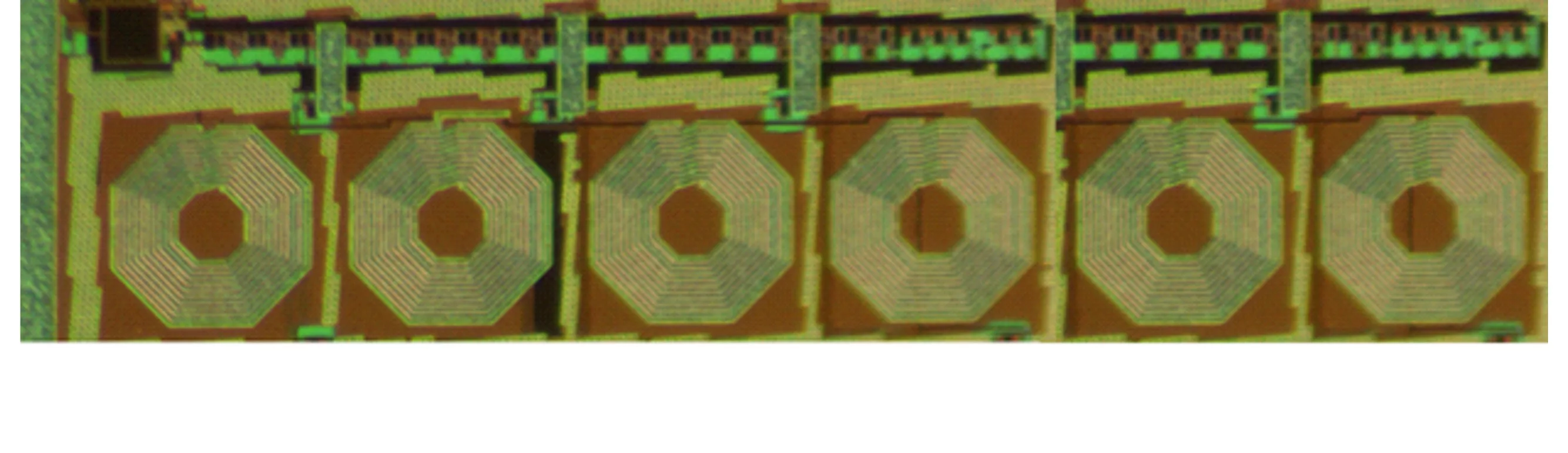

Block Diagram

Benefits

- Revolutionary Ultra Low Phase Noise operation

- Ultra Low Power Operation

- RF front end sensitivity enhancement

- Analog front end sensitivity enhancement

- Cascade-able design

Applications

- Ultra-Low Noise Multi-Stage RF Amplifier-LNA

- Ultra-Low Phase Noise Spurious PLL Filter

What’s Included?

- Behavioral Model

- Datasheet

- .gds view

- LEF view

- 2 to 3 week custom spin time

- Customizable Circuit Design

- Design Support

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Amplifier IP core

Powering the Future of RF: Falcomm and GlobalFoundries at IMS 2025

Real-Time ESD Monitoring and Control in Semiconductor Manufacturing Environments With Silicon Chip of ESD Event Detection

Novel Trade-offs in 5 nm FinFET SRAM Arrays at Extremely Low Temperatures

Linearity Analysis of Source-Degenerated Differential Pairs for Wireline Applications

How to Elevate RRAM and MRAM Design Experience to the Next Level

Frequently asked questions about Amplifier IP cores

What is Revolutionaly Ultra Low Phase Noise RF Amplifier-LNA IP?

Revolutionaly Ultra Low Phase Noise RF Amplifier-LNA IP is a Amplifier IP core from CurrentRF listed on Semi IP Hub.

How should engineers evaluate this Amplifier?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Amplifier IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.