IP for Intel Foundry

Welcome to the ultimate

IP

for

Intel Foundry

hub! Explore our vast directory of

IP

for

Intel Foundry

All offers in

IP

for

Intel Foundry

Filter

Compare

21

IP

for

Intel Foundry

from

5

vendors

(1

-

10)

-

LPDDR6/5X/5 PHY V2 - Intel 18A-P

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

-

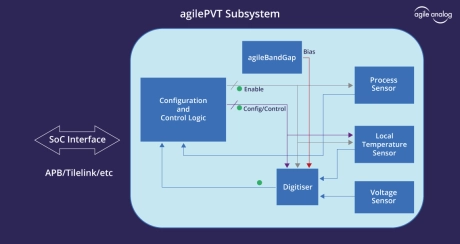

PVT Sensor Subsystem

- Start-up time: Typ 20us

- Current consumption: Max 25uA

- Industry standard digital interface

- Fully integrated macro

- Standard AMBA APB interface

-

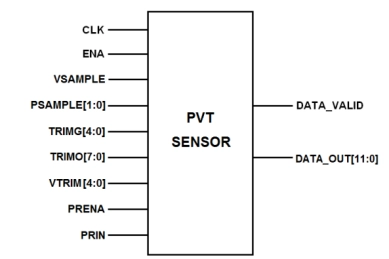

PVT Sensor on INTEL 16

- The PVT Sensor is a highly integrated macro for monitoring process, voltage, and temperature variation on-chip, allowing very high precision even in untrimmed usage.

- It consumes very little power even in operational mode, and leakage power only when measurement is complete.

-

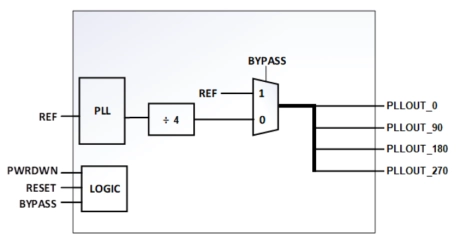

4-Phase LC PLL on INTEL 16

- High performance design for meeting low jitter requirements including Ref Clock applications

- Implemented with Analog Bits’ proprietary LC architecture

- Low power consumption

- Integrated power supply regulation for low deterministic jitter

-

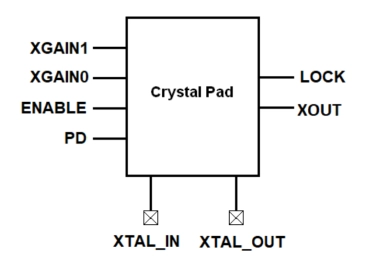

18-40MHz Crystal Oscillator on INTEL-16

- Crystal Oscillator pad macro that supports many industry standard crystals in the 18-40MHz range (e.g. 19.2, 24MHz, 25MHz, 38.4MHz)

- Uses standard CMOS transistors

- Crystal Oscillation Mode: Fundamental

- Power down option for IDDQ testing

-

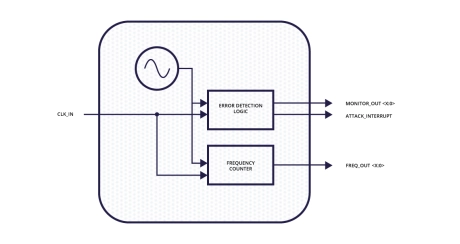

Clock Attack Monitor

- The agileCAM is a Ring Oscillator (RO) based clock attack monitor designed to detect clock attacks due to violation of the set-up time requirements of critical circuits.

- agileCAM can detect attacks based on changes in clock frequency, clock hold and clock glitch errors.

- Additionally, it provides a relative frequency measurement of the monitored clock with programmable alarm thresholds.

-

-

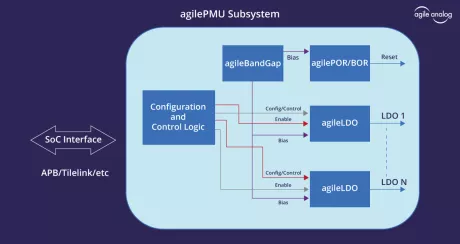

Power Management Subsystem

- The agilePMU Subsystem is an efficient and highly integrated Power Management Unit for SoCs/ASICs.

- Featuring a Power-On-Reset (POR), multiple Low Drop-Out (LDO) regulators, and an associated reference generator.

- The agilePMU Subsystem is designed to ensure low power consumption while providing optimal power management capabilities.

-

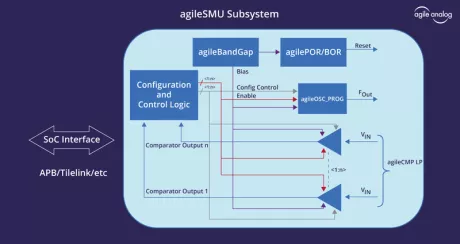

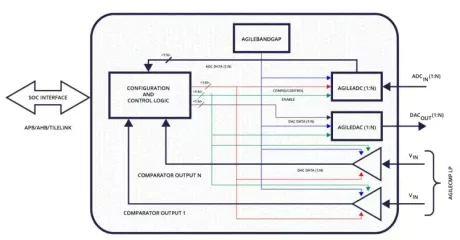

Sensor Interface Subsystem

- The agileSensorIF Subsystem is an efficient and highly integrated sensor interface for SoCs/ASICs.

- Featuring multiple Analog-to-Digital Converters (agileADC), Digital-to-Analog Converters (agileDAC), low-power programmable analog comparators (agileCMP_LP), and an associated reference generator (agileREF).

- The agileSensorIF Subsystem enables easy interaction with the analog world.

-

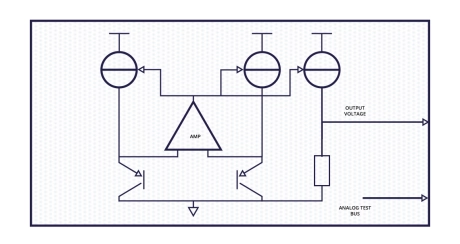

Temperature Sensor (Analog Output)

- The agileTSENSE_A GP Temperature Sensor is a traditional ΔVBE temperature sensor that amplifies the difference between two VBE voltages, and converts the result to a single-ended signal.

- This temperature sensor can be used with the agileADC in order to provide a digital output with an overall relative accuracy of +/-0.25°C.

- On modern SoCs, thermal management is critical for detection of security attacks and optimization of power, performance and area.