CCSDS IP Core

Welcome to the ultimate CCSDS IP Core IP hub! Explore our vast directory of CCSDS IP Core IP

All offers in

CCSDS IP Core

Filter

Compare

28

CCSDS IP Core

from

9

vendors

(1

-

10)

-

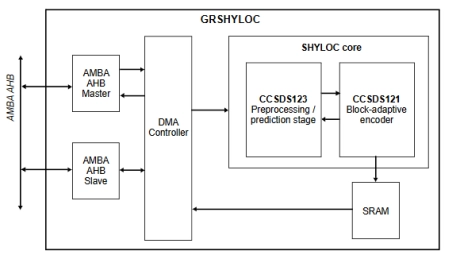

CCSDS 121/123 Lossless Compression

- The GRSHYLOC IP enables lossless compression for multi-spectral and hyper-spectral images according to the CCSDS121 and CCSDS123 standards.

- The IP features a DMA engine to fetch the raw image and store the compressed bitstream from/to external memory through the AMBA AHB master interface.

-

CCSDS ECSS

- The CCSDS/ECSS Spacecraft Data Handling IP cores represent a collection of cores that have been developed specifically for the space sector.

- These IP cores implement functions commonly used in spacecraft data handling and management systems. Supporting Software Libraries and EGSE equipment are available.

-

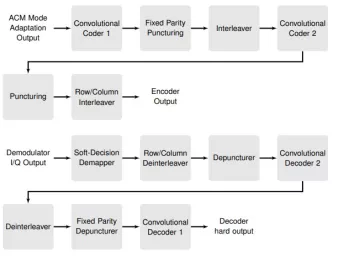

CCSDS SCCC Turbo Encoder and Decoder

- Burst-to-burst on-the-fly configuration

- High payload block length granularity (between 5,758 and 43,678 bits)

- High code rate granularity (code rates between 0.36 and 0.90)

- Configurable amount of turbo decoding iterations for trading off throughput and error correction performance

-

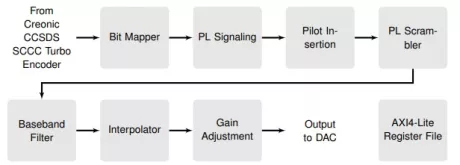

CCSDS 131.2 Wideband Modulator

- Compliant with CCSDS 131.2-B-1

- Supports ACM mode

- Supports roll-off factors 5%, 10%, 15%, 20%, 25% to 35%

-

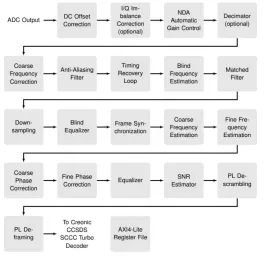

CCSDS 131.2 Wideband Demodulator

- Compliant with CCSDS 131.2-B-1

- Supports ACM mode

- Supports roll-off factors 5%, 10%, 15%, 20%, 25% and 35%

- Support for blocks with pilots only

-

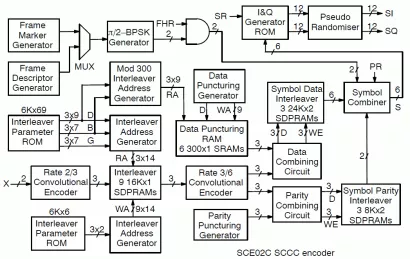

CCSDS SCCC Encoder

- 4 state CCSDS compatible serially concatenated convolutional code (SCCC) encoder

- Code rates from 0.355 to 0.899

- Data lengths from 5758 to 43678 bits

- Interleaver sizes from 8640 to 65520 bits

-

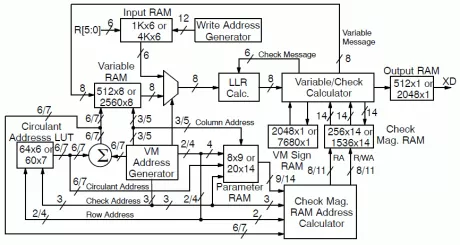

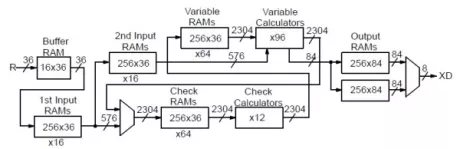

CCSDS (8160,7136) LDPC Decoder

- CCSDS compatible

- Rate 223/255 (8160,7136)

- Includes ping-pong input and output memories

- Up to 488 MHz internal clock

-

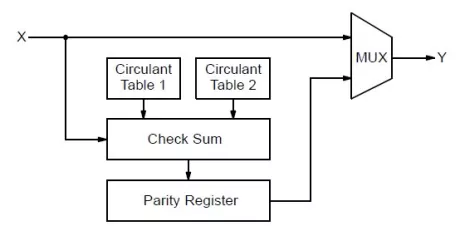

CCSDS (8160,7136) LDPC Encoder

- CCSDS compatible

- Rate 223/255 (8160,7136)

- Up to 600 MHz internal clock

- Up to 4.18 Gbit/s input data rate

-

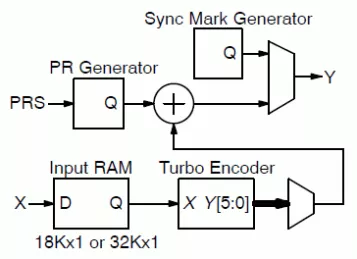

CCSDS turbo encoder with sync marker, pseudo randomiser and input memory

- 16 state CCSDS compatible turbo encoder

- Rate 1/2, 1/3, 1/4 and 1/6

- Interleaver sizes from 1784 to 16056 bits in multiples of 1784

-

CCSDS Rate 1/2 TC and TM LDPC Decoder

- CCSDS TC and TM compatible

- Rate 1/2

- Data lengths of TC 64 and 256 or optional TM 1024 bits

- Includes ping-pong input and output memories