Other

All offers in

Other

Filter

Compare

9

Other

from

8

vendors

(1

-

9)

-

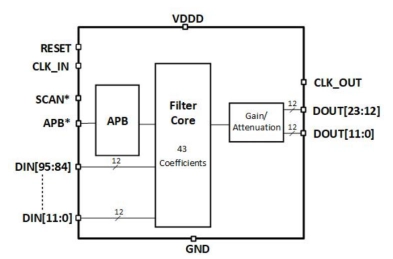

12-bit 250MHz Decimation filter with 43 taps

- Programmable Coefficients

- Programmable gain/attenuation at the output

- 4X Decimation Factor

-

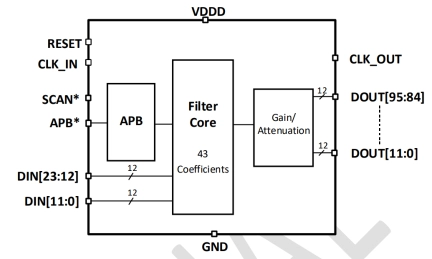

12-bit 250MHz interpolation filter with 43 taps on TSMC 16nm

- The ODT-DSP-INT-43T250M-T16 is a 12-bit 250MHz interpolation filter with 43 taps in a 12/16nm CMOS process.

- The 43 Tap interpolation filter increases output data rate (fDOUT) to the DAC by four relative to its original input data rate(fDIN).

-

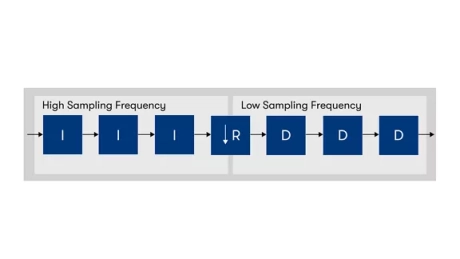

CIC Intel® FPGA IP Core

- The CIC Intel FPGA IP core implements a Cascaded integrator-comb (CIC) filter with data ports that are compatible with the Avalon® streaming (Avalon-ST) interface

- CIC filters (also known as Hogenauer filters) are computationally efficient for extracting baseband signals from narrow-band sources using decimation

- They also construct narrow-band signals from processed baseband signals using interpolation.

-

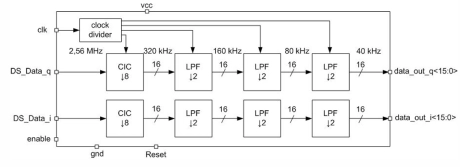

2.56 MHz Digital filter

- SGB25V technology

- Build-in clock former

- Test modes – digital data output

- Operating with complex signal

-

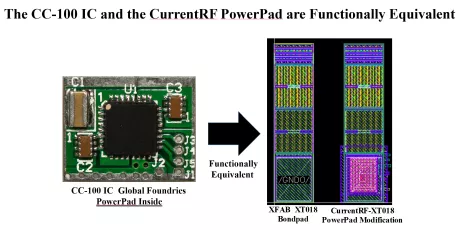

Power and Ground BondPads that include CC-100IP Digital and Switching Circuit Power Reduction Technology, Featuring 20% to 40% Total Dynamic Power Reduction

- 20% to 40% Digital and Dynamic Power Reduction

- Fits into any IC bondpad

-

-

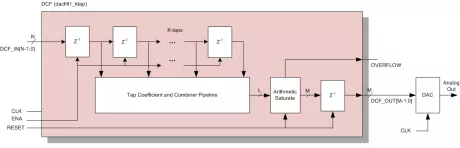

DAC Correction Filter

- Efficient, multiplier-free design

- Configurable input and output widths

- Multiple tap-length configurations

-

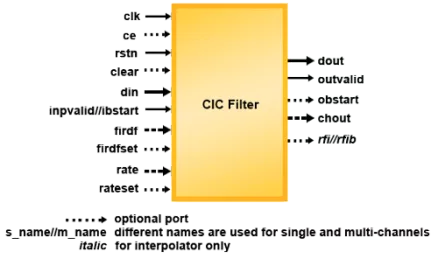

Cascaded Integrator-Comb (CIC) Filter

- 1-32-bit Input Data Width

- 1-8 Cascaded Stages

- 1-4 Cycles Differential Delay, Run-time Programmable for Both Decimation and Interpolation

- 2-16,384 Decimation and Interpolation Sampling Rate Factor, Run-time Programmable Rates for Both Decimationand Interpolation

-

Fast sort IP core

- Special sorting block for hardware implementation

- Low resources requirements

- One clock signal requirements

- Sorted array on each clock cycle