PCI-to-PCI Bridge

Key Features

- Fully supports PCI bus specification 2.2 and PCI bridge specification 1.1.

- Designed for ASIC and PLD implementations.

- Fully static design with edge triggered flip-flops.

- Independent asynchronous PCI clocks on primary and secondary bus.

- Convert bus transactions between primary bus and secondary bus.

- Combined bus master and target functions on both primary bus and secondary bus.

- Master function

- Initiate PCI memory and IO read/write

- Automatic transfer restart on target retry and disconnect

- Initiate type 0 and type 1 configuration access on secondary bus

- Target function

- Memory or IO read/write

- Receives type 0 and type 1 configuration access on primary bus

- Posted memory write transaction and delay transaction on all other transaction types

- Master function

- Dual write buffer on each direction supports posted memory write.

- Supports prefetchable and non-prefetchable memory read.

- Delay transaction processes IO read/write, configuration read/write and memory read transactions.

- Supports target retry, disconnect, master abort and target abort terminations.

- Parity generation and parity error detection.

- Includes all PCI-PCI bridge specific configuration registers.

- Supports high speed bus request and bus parking.

- Optional PCI bus arbiter with fix, rotating, and custom priority.

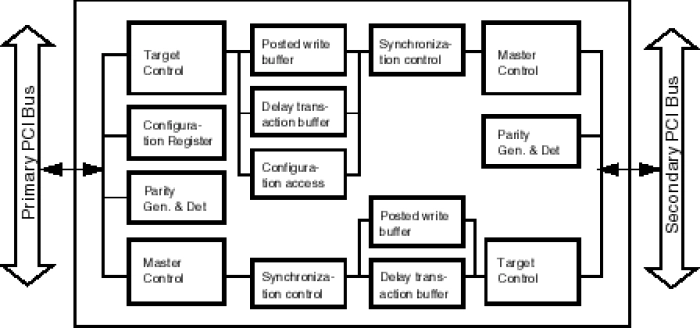

Block Diagram

Technical Specifications

Short description

PCI-to-PCI Bridge

Vendor

Vendor Name

Foundry, Node

ASIC and FPGA

Availability

Now