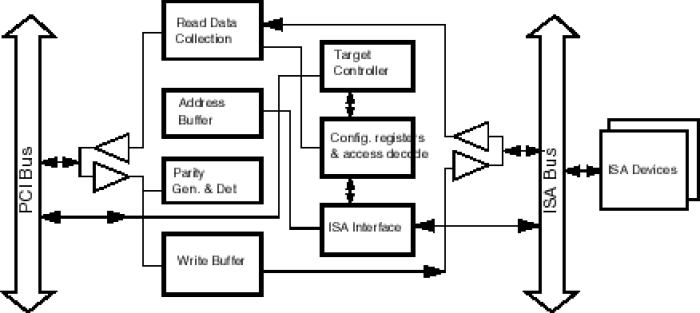

PCI-ISA Bridge

Key Features

- Compliant with PCI bus specification 2.1 and 2.2.

- Convert PCI transaction to ISA bus transaction.

- Function as PCI target on PCI bus.

- Function as ISA master on ISA bus.

- Map PCI address space to ISA address space through Base Address Register.

- Supports 16-bit and 8-bit data transfer, memory and IO transfers on ISA bus.

- ISA bus operates on one-fourth the frequency of the PCI clock.

- Performs multiple ISA operations to transfer each 32-bit PCI word.

- Write buffer to speed up PCI-to-ISA write transfer.

- Support ISA devices with different speed by using NOWS# and CHRDY signals.

- Parity generation and parity error detection on PCI bus.

- Includes all PCI specific configuration registers.

- Fully synchronous design, no gated clock or transparent latch. All flip-flops are rising edge trigger.

Block Diagram

Technical Specifications

Short description

PCI-ISA Bridge

Vendor

Vendor Name

Foundry, Node

ASIC & FPGA

Availability

now