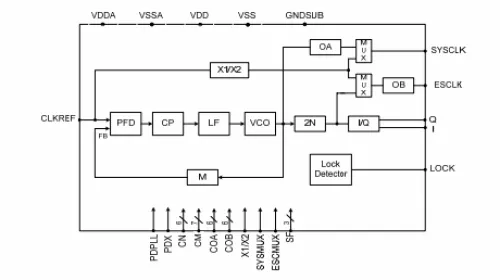

The MXL-PLL-MIPI-PXL is a high performance PLL based frequency synthesizer implemented using digital CMOS technology. It is highly integrated and requires no external components. Differential circuit techniques are employed to attain low jitter in the noisy environment typical of multi-million gates digital chip.

The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design. The MXL-PLL-MIPI-PXL incorporates a Lock Detector, three programmable output dividers, and supports a full-power down mode.

MIPI PLL

Overview

Key Features

- All output programmable dividers produce 50% duty cycle for both even and odd divisors

- High performance, highly programmable MIPI Pixel PLL

- Digital CMOS process

- Low power dissipation

- No external components required

- High frequency, low jitter output

- Three programmable output frequencies

- Glitch-free transition outputs

- Wide input frequency range

- Integrated Lock detector

- Full power-down mode

- Buffered programmable dividers

Block Diagram

Applications

- Mobile

- Displays

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- Timing Model

- Integration Guidelines

- Documentation

- One year support

Technical Specifications

Foundry, Node

All, Upon Request

Maturity

Upon Request

Availability

Upon Request

SMIC

Pre-Silicon:

130nm

LL

TSMC

Pre-Silicon:

40nm

LP

,

130nm

G

Silicon Proven: 65nm LP

Silicon Proven: 65nm LP

Tower

Pre-Silicon:

180nm