The MXL-PLL-CDR is a clock/data recovery PLL implemented using a digital CMOS process. It is highly integrated and require no external components. Differential circuit techniques are employed to attain low jitter in the noisy environment typical of multi-million gates digital chip.

The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

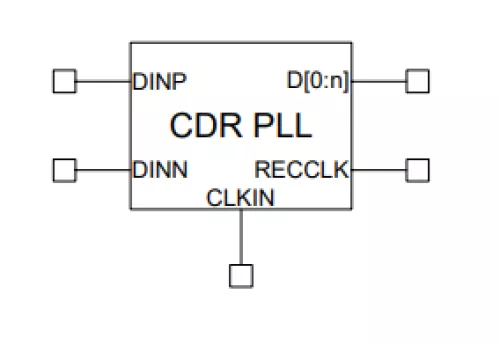

Clock/Data Recovery PLL

Overview

Key Features

- High performance, clock and data recovery PLL

- Digital CMOS processes

- Low power dissipation

- No external components required

- High frequency, low jitter output

- Modular design to facilitate customization and process migration

- Performance is superior to that obtained using over sampling techniques

Block Diagram

Applications

- Mobile

- Displays

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- Timing Model

- Integration Guidelines

- Documentation

- One year support

Technical Specifications

Maturity

Silicon Proven

Availability

Upon Request

GLOBALFOUNDRIES

Silicon Proven:

130nm

SMIC

Pre-Silicon:

130nm

LL

,

180nm

LL

TSMC

Pre-Silicon:

130nm

G

,

180nm

G

Silicon Proven: 130nm LVOD , 180nm LV

Silicon Proven: 130nm LVOD , 180nm LV