Clock and Data Recovery of HDB3/B3ZS coded signals

An all-digital solution suitable for clock/data recovery of HDB3/B3ZS coded signals.

Overview

An all-digital solution suitable for clock/data recovery of HDB3/B3ZS coded signals.

Key features

- Performs receive clock and data recovery on HDB3/B3ZS coded data.

- Programmable jitter attenuator.

- Loss of signal detection.

- Frequency aided acquisition using external reference clock.

- Fast acquisition time.

- Narrow bandwidth digital phase locked Loop.

- NCO used for an all-digital implementation.

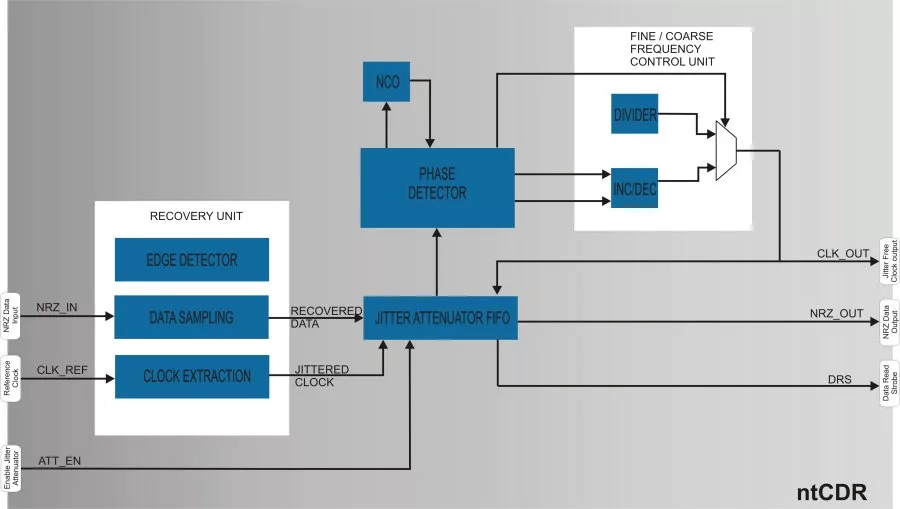

Block Diagram

What’s Included?

- Synthesizable VHDL or Verilog source code.

- VHDL or Verilog test bench with example configuration files.

- Synthesis scripts.

- Users manual.

- Free 3 months technical support.

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 180nm | BCDG2 | Silicon Proven |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is Clock and Data Recovery of HDB3/B3ZS coded signals?

Clock and Data Recovery of HDB3/B3ZS coded signals is a Single-Protocol PHY IP core from Noesis Technologies listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.