Low Bandwidth PLL IP

Welcome to the ultimate Low Bandwidth PLL IP hub! Explore our vast directory of Low Bandwidth PLL IP

All offers in

Low Bandwidth PLL IP

Filter

Compare

8

Low Bandwidth PLL IP

from

4

vendors

(1

-

8)

-

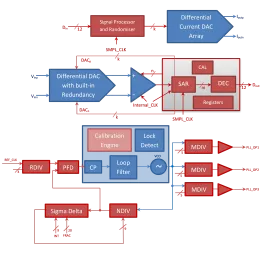

40nm 1.1V AFE comprising 12-bit IQ ADC, 12-bit IQ DAC and Clock-PLL

- Rail-to-Rail IQ ADC Input Capability

- 65dB IQ ADC SNR

- Programmable Full-Scale IQ DAC Output Current

- 65dB IQ DAC SNR

-

40nm 1.1V 6.0GHz-9.4GHz Fractional-N RF PLL

- TSMC 40nm CMOS

- 6.0GHz-to-9.7GHz Buffered VCO PLL Output Coverage

- Scalable Power Consumption

-

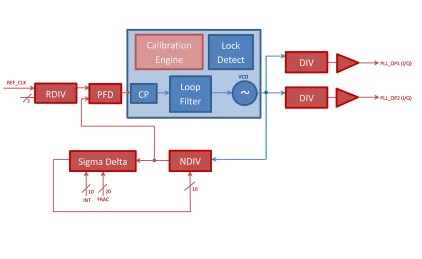

40nm 1.1V 2GHz-4.7GHz Fractional-N RF Quadrature PLL

- 2.0GHz-to-4.7GHz PLL Output Coverage

- Scalable Power Consumption

-

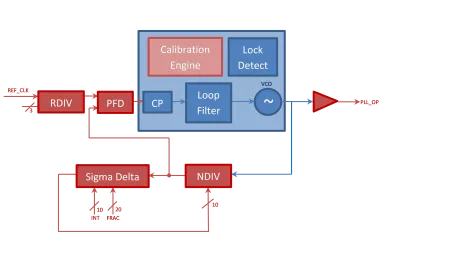

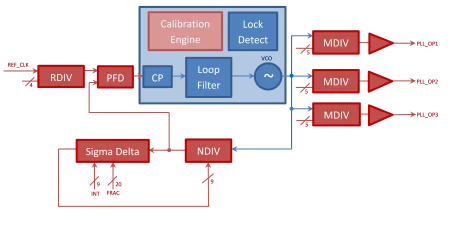

40nm 1.1V 16MHz-2GHz Fractional-N Clock-PLL

- 16MHz-to-2GHz PLL Output Coverage

- Scalable Power Consumption

- Three independent programmable PLL outputs

- Internal Calibration Engine and Convergence Algorithm

-

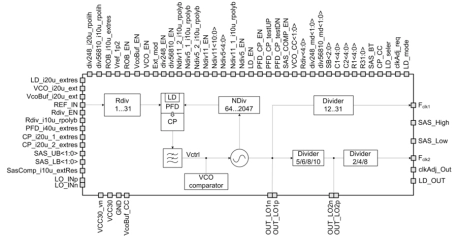

1.68 to 1.917 GHz Phase-Locked Loop

- AMS SiGe BiCMOS 0.35um

- Reference frequency from 10MHz to 125MHz

- LO1 frequency range from 1.692GHz to 1.973GHz

- LO2 frequency range from 175MHz to 225MHz

-

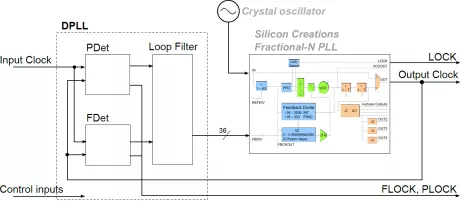

High Quality LC-PLLs

- Automatically locks over an extremely wide input frequency range

- Dual-loop P

- Wideband integrated jitter <400fs in integer mode, <800fs in fractional mode with high-speed / clean reference with active fractional noise cancellation

- Passes PCIe6 reference clock requirements with wide margin

- Reference spur <200fs RMS

- Random period jitter <30fs RMS

- LL effective loop bandwidth can be arbitrarily small

-

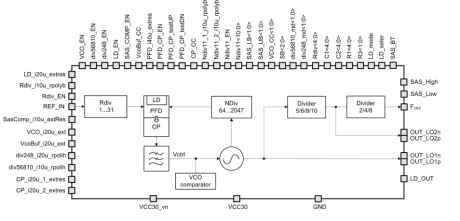

1.013 to 1.217 GHz phase-locked loop

- AMS SiGe BiCMOS 0.35um

- Reference frequency from 10MHz to 125MHz

- LO1 frequency range from 1.013GHz to 1.127GHz

-

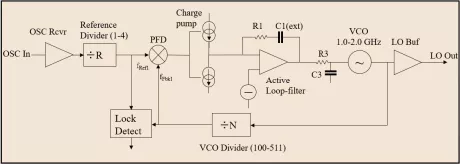

Integer N PLL for Frequency Synthesis

- 1 GHz–2 GHz LO frequency range

- 5 MHz–20 MHz input clock frequency range

- 9-bit programmable divider (100-511)

- 7-band VCO with off-chip resonator