Clock Generator PLL IP

Welcome to the ultimate Clock Generator PLL IP hub! Explore our vast directory of Clock Generator PLL IP

All offers in

Clock Generator PLL IP

Filter

Compare

407

Clock Generator PLL IP

from

16

vendors

(1

-

10)

-

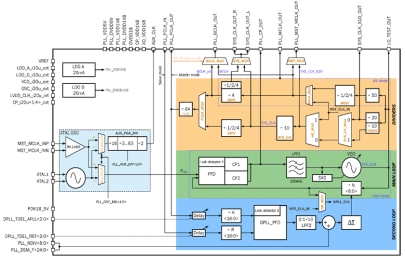

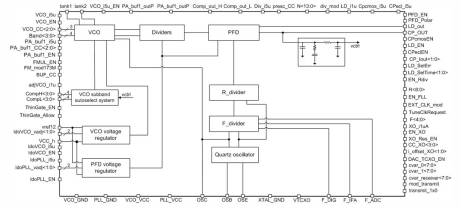

2.26GHz/2.46GHz Fractional-N LC Phase-Locked Loop with oscillator

- 180XFAB_PLL_01 uses 2.25792GHz/2.4576GHz Phase locked loop frequency synthesizer for clock generation.

- It consists of the following main sub-blocks: reference oscillator; main PLL loop: Fractional-N PLL and VCO blocks; secondary digital PLL loop: synchronization subsystem; dividers block: clock generation/delivery subsystem; voltage stabilizers.

- High frequency synthesis is needed for both phase noise performance and ultra-fine frequency tuning step.

-

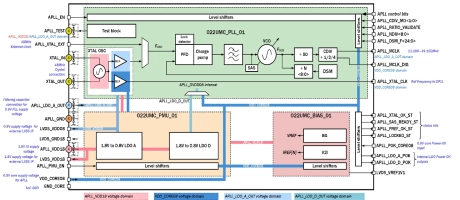

10MHz to 50MHz fractional-N PLL synthesizer

- UMC 22nm ULP technology

- 1.8V IO power supply

- Double 0.8/1.0V Core power supply

- Embedded low noise bias

-

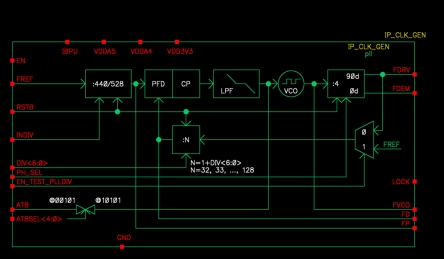

Integer-N-PLL-based HF Frequency Synthesizer and Clock Generator with integrated Loop Filter and VCO

- This integer-N PLL synthesizes 3.3V-square-wave FVCO frequencies within the HF range from 2.424MHz up to 9.697MHz, by steps of 18.9393kHz, and provides one fourth of fVCO on two other outputs, FDEM and FDRV, which feature quadrature phase difference or no phase shift depending on the control bit PH_SEL.

- The PLL-locked state within ±0.08% of fVCO is signaled by a logic high level on the LOCK output.

-

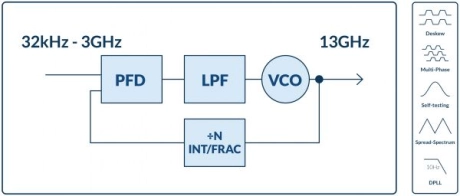

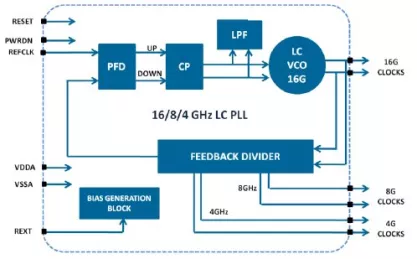

High Speed 16GHz PLL

- Type II ,3rd order low jitter PLL

- Auto calibration for process and temperature (USP)

- Programmable frequency using CSR registers

- 8/10/16GHz quadrature clocks

- Operating temperature -40 to 125

-

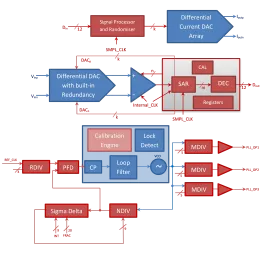

40nm 1.1V AFE comprising 12-bit IQ ADC, 12-bit IQ DAC and Clock-PLL

- Rail-to-Rail IQ ADC Input Capability

- 65dB IQ ADC SNR

- Programmable Full-Scale IQ DAC Output Current

- 65dB IQ DAC SNR

-

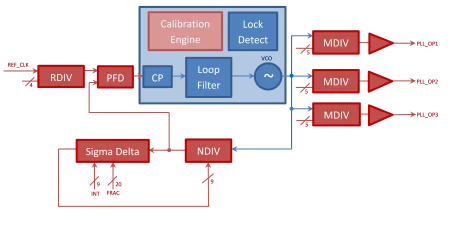

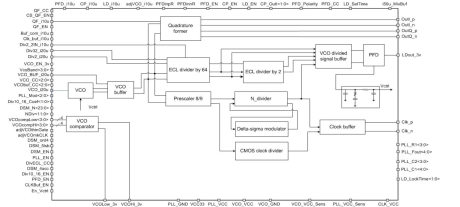

40nm 1.1V 16MHz-2GHz Fractional-N Clock-PLL

- 16MHz-to-2GHz PLL Output Coverage

- Scalable Power Consumption

- Three independent programmable PLL outputs

- Internal Calibration Engine and Convergence Algorithm

-

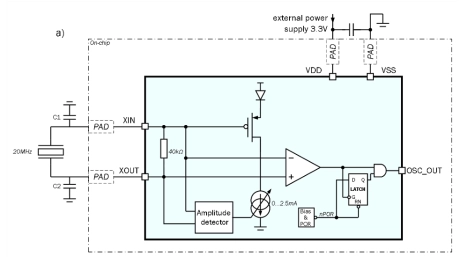

10 to 40 MHz crystal oscillator

- Supply voltage 3.3V

- Output frequency 10-40MHz

- GF 180nm MCU CMOS technology

-

Phased-locked loop 120 to 950 MHz

- iHP SGB25V

- Wide frequency range (120…950 MHz)

- Operating frequency selection using external components

- Built-in switched capacitor sections for VCO frequency adjustment

-

Phase-locked loop system 2.8 to 3.3 GHz

- SMIC CMOS 0.18 um

- Wide frequency range (2.8…3.3 GHz)

- Built-in switched capacitors sections for VCO frequency adjustment

- Low noise figure

-

General-purpose & Specialized Ring PLLs + RTL-based Solutions

- Wide functional range allows all frequencies in a system to be synthesized with one PLL macro

- Input & output frequency ranges greater than 1000:1