12-Bit ADC IP

12-Bit ADC IP cores come in various speeds, use different interfaces, and provide differing degrees of accuracy. The most common types of ADCs are flash, successive approximation, and sigma-delta.

The vendors support all the major foundries including TSMC, GlobalFoundries, Intel Foundry, Samsung Foundry and UMC.

All offers in

12-Bit ADC IP

Filter

Compare

208

12-Bit ADC IP

from

38

vendors

(1

-

10)

-

Ultra high-performance low-power ADC

- TSMC 28nm

- Ultra high-performance low-power ADC

- 12-bit ADC resolution

- Sampling rate up to 5GSPS

-

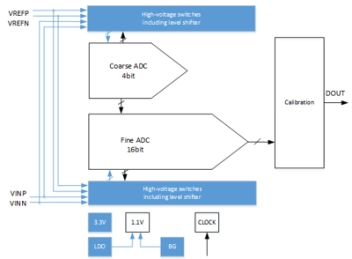

12-bit/16-bit SAR ADC

- 12 bits 100Msps SAR ADC on 28nm process;

- 12 bits 25Msps SAR ADC and Pipeline ADC above 100Msps on 40/55nm process;

- 16 bits 2/1Msps SAR ADC on 40/55nm process;

-

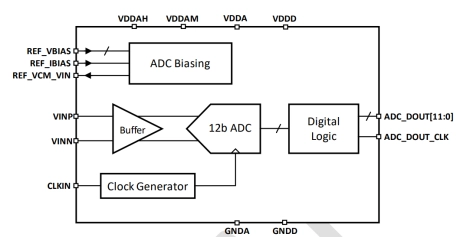

12-bit 400MSPS ADC on TSMC 7nm

- The ODT-ADS-12B2400M-7T is an ultra low power ADC designed for use in a 6/7nm CMOS process.

- This 12-bit, 400MSPS ADC supports input signals up to 200MHz and features a differential full-scale range of 1.0Vpp and excellent static and dynamic performance.

-

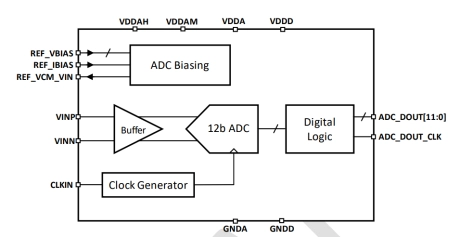

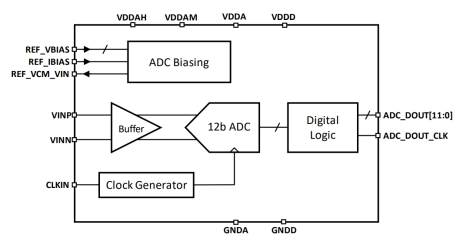

12 bit, 200 MSPS ADC on TSMC 16nm FFC

- The ODT-ADS-12B200M-16FFCT is an ultra low power ADC designed in a 16nm CMOS process.

- This 12-bit, 200MSPS ADC supports input signals up to 100MHz and features a differential full-scale range of 1.0Vpp and excellent static and dynamic performance.

-

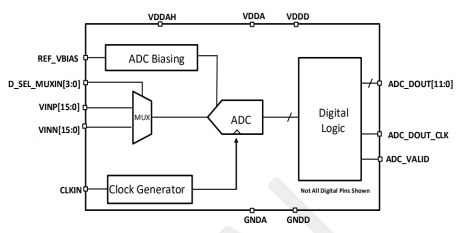

12-bit, 5 MSPS ADC with 8:1 Input Mux in a TSMC 6nm

- The ODT-ADS-12B5M-6T is an ultra-low-power, high-linearity ADC with rail-to-rail inputs designed in a TSMC 6nm process.

- This 12-bit, 5MSPS ADC supports input signals up to 1 MHz and features excellent static and dynamic performance.

- The input front-end includes a mux that can support 16 single-ended or differential inputs.

-

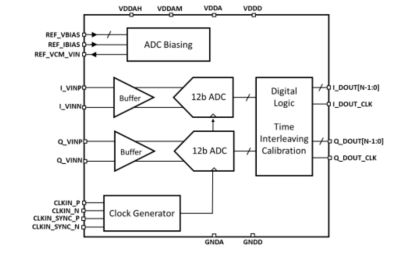

12-bit, 4 GSPS High Performance IQ ADC in GF22FDX

- GF22FDX Process

- 12-bit resolution, 4GSPS update rate

- Dual ADC configured as IQ Pair

-

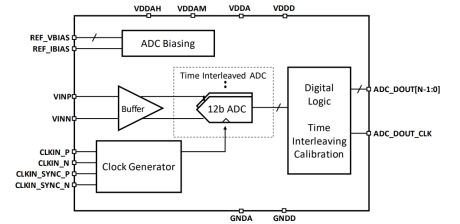

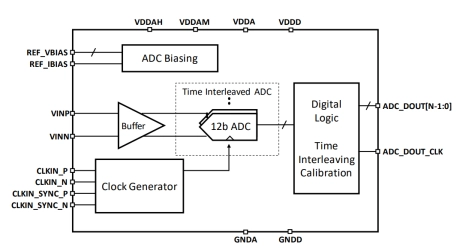

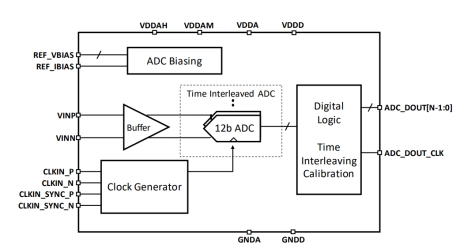

12-bit, 8 GSPS ADC in 7nm CMOS

- The ODT-ADS-12B8G-7nm is an ultra-highperformance time-interleaved ADC designed in a 7nm CMOS process.

- This 12-bit, 8GSPS ADC supports input signals up to 2.5 GHz and features a differential fullscale range of 0.8Vpp and excellent static and dynamic performance.

-

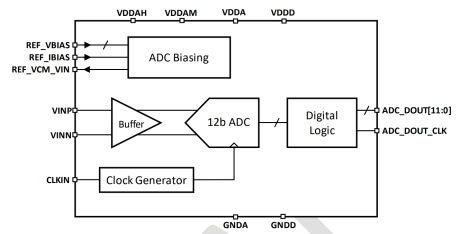

12 bit, 500 MSPS ADC on GF 22FDX

- The ODT-ADS-12B500M-G22FDX is an ultra-low power ADC designed in a 22nm CMOS process.

- This 12-bit, 500MSPS ADC supports input signals up to 100MHz and features a differential full-scale range of 0.8Vpp and excellent static and dynamic performance.

- The ADC architecture is optimized to maximize performance while minimizing power and area consumption. The ADC includes an integrated input buffer.

-

12-bit, 8 GSPS High Performance ADC in 16nm CMOS

- The ODT-ADS-12B8G-16 is an ultra highperformance time-interleaved ADC designed in a 16nm CMOS process.

- This 12-bit, 8GSPS ADC supports input signals up to 3.0 GHz and features a differential fullscale range of 0.8Vpp and excellent static and dynamic performance.

-

12 bit 250MSPS ADC on TSMC 7nm

- The ODT-ADS-12B250M-7T is an ultra-low power ADC designed in a 7nm CMOS process.

- This 12-bit, 250MSPS ADC supports input signals up to 100MHz and features a differential full-scale range of 0.8Vpp and excellent static and dynamic performance.