Seven Powerful Reasons Why Menta eFPGA Is the Clear Choice for A&D ASICs

By Menta

The value of eFPGA (embedded FPGA) in aerospace and defense ASICs lies in its in-system reconfigurability, long lifecycle adaptability, and mission-specific flexibility. Applications span a broad spectrum – from radar and communications systems to electronic warfare, unmanned aerial vehicles, connected battlefield technologies, and space-based platforms. Across these diverse use cases, adaptable hardware is essential for delivering high-performance, real-time processing capable of handling multiple high-speed inputs and sensor data simultaneously. This flexibility not only enhances mission effectiveness but also extends the operational life and value of critical systems. Let’s take a closer look at how eFPGA enables these advantages.

Solution #1 – Reconfigurability for Long Lifecycle Platforms

Aerospace and defense systems can often operate for 10-30 years. eFPGA allows hardware-level updates post deployment enabling bug fixes, algorithm enhancements and support for new protocols, encryption or compression standards. For example, take modern radar platforms must support multiple roles – such as surveillance, tracking, and jamming resistance – on a single platform. Adaptable hardware (e.g., eFPGA) allows dynamic reconfiguration based on mission needs, without requiring new silicon. Radar systems often require low-latency, high-throughput DSP (Digital Signal Processing). As threat environments change or new waveforms are introduced, adaptable hardware allows on-the-fly updates to filter banks, reprogramming of beamforming logic, dynamic modulation/demodulation adjustments. Threats evolve rapidly, and radar systems must adapt their response – jamming avoidance, stealth detection, pulse agility, etc. Reprogrammable logic ensures systems remain effective without a full redesign.

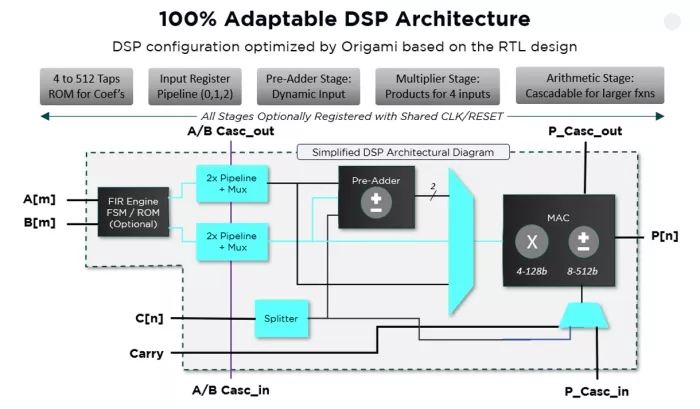

Menta eFPGA delivers two key advantages for signal processing applications. First, unlike fixed-function DSP blocks with constrained data widths, Menta’s fully configurable DSP architecture allows you to tailor the precision, width, and structure to match your exact signal processing requirements – eliminating overdesign and improving efficiency.

Figure 1 – 100% Adaptable DSP Solution

Second, Menta enables the integration of tightly coupled 3rd-party memory, ideal for high-performance buffering and coefficient storage in filter designs. This co-optimized approach maximizes both performance and silicon area, ensuring your implementation is finely tuned to your project’s specific needs.

Solution #2 – Security and Crypto Agility

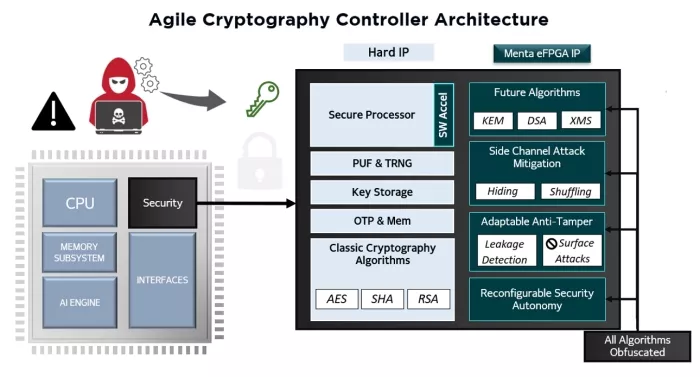

Defense applications require field-upgradable cryptographic solutions to stay ahead of rapidly evolving threats. Adaptable hardware enables post-quantum cryptography readiness, secure key management, and hardware root-of-trust – allowing in-hardware updates without the need for full system re-spins. It also provides the flexibility to counter emerging side-channel and anti-tamper threats in an era where adversaries are more motivated and better equipped than ever.

Figure 2 – Agile Security Enclave enabled by Menta eFPGA

While many aerospace and defense organizations depend on fixed third-party security IP, this often limits their flexibility and ties them to external providers. eFPGA empowers security autonomy by enabling tailored, mission-specific protection with additional layers of defense. Notably, all security logic implemented in eFPGA benefits from an inherent layer of obfuscation – since the fabric is erased at power-down, attackers are left with nothing but an unconfigured matrix of logic gates.

Menta’s eFPGA offers two distinctive advantages: First, every Menta eFPGA implementation is unique, traceable through embedded watermarks, blockchain-based identifiers, and digital certificates – ensuring complete isolation between customer designs and making reverse-engineering virtually impossible. Second, Menta’s configuration logic is a simple, resettable D-flip-flop chain that can be fully erased in a single clock cycle – enabling immediate mitigation in response to intrusion detection.

Menta’s architecture is further strengthened by proven integrations with leading security IP partners, delivering trusted and adaptable solutions for the most demanding defense environments. Read more about how Menta’s eFPGA IP enables true security in ASICs and SoCs in this blog – Nine Compelling Reasons Why Menta eFPGA Is Essential for Achieving True Crypto Agility in Your ASIC or SoC.

Solution #3 – Adaptability to Regional or Missions-Specific Requirements

Hardware can be reconfigured to meet different export control regulations, frequency bands, or mission-specific logic without changing the ASIC. Ideal for platform reuse across NATO and non-NATO markets or across different mission profiles. This also accelerates time-to-market, as critical IP can be finalized even after tape-out. Design changes and iterations come at no additional silicon cost – eliminating the need for expensive and time-consuming ASIC respins

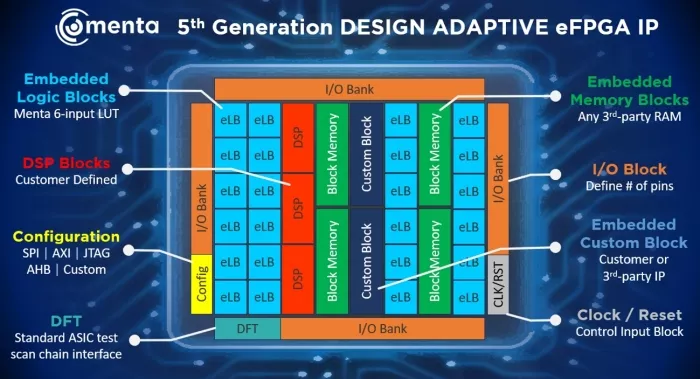

Another unique advantage of Menta eFPGA is its complete configurability – you can define the logic density, DSP capabilities, and memory resources to meet your exact requirements. Menta also supports the integration of custom embedded blocks directly into the fabric, enabling tight coupling of critical hard IP with the reprogrammable array for optimized performance and efficiency.

Figure 3 – Menta’s 5th Generation eFPGA IP Architecture

Unlike hard IP solutions—which are rigid, slow to deliver, and can take up to a year—Menta’s soft IP can be delivered in just a few weeks. Even more importantly, if changes are needed downstream, Menta can implement and deliver updated IP within days. In contrast, any modification to a hard IP typically resets the entire design timeline, forcing a complete restart of the process and can create significant project delays.

Solution #4 – SWaP-C Optimization

Compared to standalone FPGAs, eFPGA offers significant advantages: it reduces board footprint, lowers power consumption, and significantly cuts BOM costs. It also removes dependence on vulnerable supply chains, avoids part obsolescence and price inflation of “mature” devices, and mitigates downstream security risks associated with discrete components. Discrete FPGAs, by nature of their external accessibility, are more susceptible to interception, cloning, and tampering. By integrating Menta eFPGA, customers can precisely customize logic, memory, and DSP resources to meet their exact product requirements – enhancing performance, security, and design efficiency.

Table 1 – Value Integrating eFPGA vs. Using a Discrete FPGA

| Feature | eFPGA (Embedded FPGA) | FPGA (Discrete FPGA) |

| Integration | Integrated into SoC/ASIC | Separate chip on PCB |

| Latency | Very low (on-chip communication) | Higher (off-chip communication adds delays) |

| Power Consumption | Lower (no high-speed I/O needed), Optimized to your node | Higher (external I/Os consume more power) |

| Footprint | Smaller (no external chip needed) | Larger (requires board space) |

| Performance | Faster due to direct internal connections | Slower due to I/O bottlenecks |

| Customization | Custom-sized logic blocks for specific applications | Fixed sizes defined by manufacturer |

| Cost (per unit) | Lower for high-volume ASICs (saves on BOM, packaging and supplier margin) | Higher due to separate chip and I/O circuitry, subject to price increases |

| Design Time | Longer (requires SoC or ASIC integration and verification) | Shorter (off-the-shelf, ready to use) |

| Reliability | Higher (fewer components and interconnects). 100% Standard Cell – no custom logic | Lower (more failure points due to packaging and connections) |

| Supply Chain | None | Very Complex and many opportunities for corruption |

| Obsolescence | None | Subject at any time |

Solution #5 – Survivability and Autonomy

Menta’s eFPGA is built entirely from standard cells, with no custom logic – making it fully portable across any foundry, technology node, or process, including radiation-hardened libraries. Most eFPGA and FPGA providers use SRAM bitcells, while Menta uses standard D flip-flops (D-FFs)—and for good reason:

- Radiation Tolerance: D-FFs are inherently more resistant to radiation-induced bit flips. Their master-slave structure makes them less likely to corrupt from a single particle strike, unlike dense SRAM cells, which are more vulnerable due to their compact 6-transistor design. As process nodes shrink, SRAM’s susceptibility increases.

- TMR Compatibility: With D-FFs at the core, Menta’s architecture can supports Triple Modular Redundancy (TMR) for even greater resilience.

This makes it ideally suited for space-grade and mission-critical ASICs. The architecture also supports reconfiguration for adaptive fault tolerance, system redundancy, and autonomous in-field decision-making. In radiation-prone and harsh environments, eFPGA enhances both reliability and resiliency – enabling aerospace and defense ASICs to adapt, defend, and endure. The result: extended mission life, sustained relevance, and true survivability in high-risk operational scenarios.

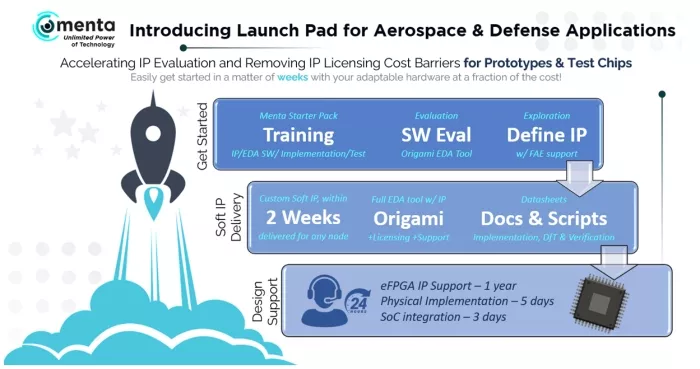

Solution #6 – Eliminating IP Licensing Cost Barriers for Prototype and Aerospace and Defense Test Chips with Menta’s LaunchPad Program

At Menta, we recognize the budget constraints that come with early-stage development for Aerospace & Defense customers, especially when building prototypes or test chips with uncertain futures. Paying full IP licensing fees at this stage can be a barrier to innovation – so we created the Menta Aerospace & Defense LaunchPad Program to eliminate that friction.

The LaunchPad Program is designed to accelerate eFPGA IP evaluation by offering deeply discounted access – up to 90% off standard licensing fees – and rapid IP delivery within just a few weeks.

We roll this out in three streamlined phases:

1. Getting Started

- Hands-on training and evaluation licenses for our Origami EDA tool

- Expert support to define architecture and IP requirements tailored to your design

2. Soft IP Delivery

- IP delivered in less than 2 weeks

- Seamless integration with Origami, including datasheets, documentation, testbenches, and implementation/verification scripts

3. Design Integration Support

- Ongoing, 24-hour support throughout physical design, DfT, and SoC integration

- Collaborative guidance to ensure first-pass success

Menta isn’t just an IP vendor – we’re your IP partner. From early evaluation through final silicon, our goal is to remove barriers, reduce risk, and help you move fast with confidence.

Figure 4 – Menta’s LaunchPad Program

Solution #7 – Menta Acceleration Partners

Bringing complex products to market is challenging – especially when each application demands a unique combination of domain expertise. At Menta, we understand this, which is why we created the Menta Acceleration Partner (MAP) Program. This ecosystem is designed to bridge the gap between raw silicon and deployable solutions, helping customers turn technology into impact – quickly and efficiently.

Our MAP network includes turnkey IC development firms like Trusted Semiconductor Solutions, renowned for their expertise in trusted, high-reliability microelectronics. They have successfully implemented Menta eFPGA across multiple technology nodes, consistently achieving target maximum clock speeds and surpassing testing thresholds well beyond the stringent requirements for space applications.

We also collaborate closely with full-service design houses like IC’Alps and Presto Engineering, both of which bring deep expertise across industrial, communications, and medical markets. In addition, the MAP program features best-in-class IP partners specializing in key areas such as security (including Synopsys, Xiphera, PQSecure, and Nagra), software acceleration (Codasip, AndesTech, Siemens), signal processing, communications, and more.

With MAP, we connect you to the right experts to help accelerate your design from concept to deployment. Just like the name suggests – it’s all about speed, scalability, and solutions.

Figure 5 – Menta’s Acceleration Partners

Conclusion

Menta eFPGA brings critical flexibility and future-proofing to Aerospace & Defense ASICs—reducing risk, enabling in-field upgrades, and extending the value and performance of mission-critical silicon.

Our soft eFPGA IP, based on 100% standard cell libraries, is uniquely:

- Foundry-independent – implementable on any process

- Fast to deploy – delivered in RTL in just days

- Cost-efficient – reduced NRE and downstream cost

- Flexible and secure – obfuscated bitstream unique to each device

- Production ready – highest yield, best testability

- Proven – silicon validated across foundries, with radiation-hardened options

- Customizable – supports 3rd party block RAMs, patented DSPs

About Menta

Menta, a pioneering leader in embedded FPGA (eFPGA) technology with over 15 years of proven success, delivers 100% standard-cell, third-party embedded FPGA IP for SoC, ASIC, and ASSP designs. As the only pure-play eFPGA provider offering silicon-proven, synthesis-free IP, Menta empowers semiconductor designers to adapt post-production — enabling rapid updates for bug fixes, customer-specific customizations, evolving standards, or enhanced security.

Our cutting-edge IP is delivered with the Origami toolchain, a seamless solution that generates bitstreams directly from RTL, streamlining design and accelerating time-to-market. Trusted by global semiconductor leaders, Menta transforms chips into agile, future-proof platforms — redefining what’s possible in silicon design.

For more information, please visit the Menta site: https://www.menta-efpga.com/

Related Semiconductor IP

- eFPGA Soft IP

- eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- eFPGA on GlobalFoundries GF12LP

- eFPGA Hard IP Generator

Related Articles

- Nine Compelling Reasons Why Menta eFPGA Is Essential for Achieving True Crypto Agility in Your ASIC or SoC

- Top 5 Reasons why CPU is the Best Processor for AI Inference

- Unlocking the Power of Digital Twins in ASICs with Adaptable eFPGA Hardware

- The Future of Embedded FPGAs - eFPGA: The Proof is in the Tape Out

Latest Articles

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks