LPDDR4: Now and for Next Generation

By Umesh Patel, Arastu Systems

Introduction

Technology has leapt several folds. Looking at the communication industry, it has steadily advanced from the heavy gadgets that had only calling and texting facilities, a poor battery life only made matters worse. This industry however has led to many research works and innovations, the phones that were once meant only for calling are now capable of doing so much, calling is now a secondary feature. Mobile device user is using so many applications in parallel which in turns demands more powerful processing unit and faster, bigger memory.

Why we need a Faster RAM

This advent of technology in terms of faster computing capabilities, clearer displays and better storage capacities to name a few goes hand in hand. For example, if the display on your phone isn't clear enough, you would ideally want to switch to a phone that has a better display. In order to achieve high resolution, the DSP processor must be more advanced in terms of sampling algorithm and speed, only then can it process the virtual signals and make them appear close to real. When the processor is fast, we would also need a RAM (Random Access Memory is the part of the memory that stores all your temporary or ‘real-time’ data, gaming and video data for an instance) that is fast enough and is high in capacity. Thus if one aspect of a computing device is faster, it is inevitable for the rest to catch up. With speed and capacity, the power dissipation must be taken care too else the battery would drain out rapidly, much to the dismay of the user.

Current Market Trends

The most widely discussed memories of the current context are LPDDR3 (Low Power Double Data Rate RAM Generation 3) and LPDDR4 (Low Power Double Data Rate RAM Generation 4). LPDDR3 is the most widely used memory in the smart portable devices owing to the bandwidth (up to 2133MB/s) and low power consumption (1.2V) and an array of power saving features such as low signaling power, that it offers. Despite being this efficient LPDDR3 is steadily being superseded by LPDDR4 as the consumers look for higher resolution displays (4K is in!) and even less battery draining products. It is quite easy for us to conclude that LPDDR4 is a faster version of LPDDR3, but it takes a lot more to double the bandwidth and reduce the power consumption by 40%. The memory architecture has been modified to achieve such numbers.

What has changed

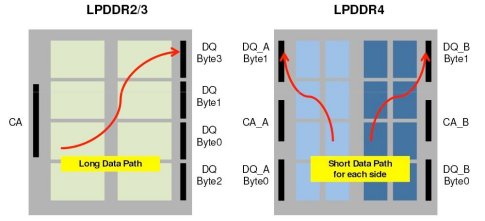

Let us take a sneak peek to see what enhancements have been done from LPDDR3 to reach the LPDDR4 stage. For LPDDR4 there is a 2-channel per die architecture that has been implemented thus the 32 data bits have now been divided into 16x2 which is 16 per channel. The PHY level signaling also has been modified to a lower voltage signaling technique (LVSTTL) that limits the signal’s peak swing to 350mV. There is also a reduction in the CA (Command-Address pins) from 10 pins to 6 pins as the CA bus is encoded. Now let us take a look at the picture below to see what advantage does the multi-channel architecture have. One would see that the CA_A and CA_B (Command Address Bus Channel A&B) to DQ_A and DQ_B (Data bus for channel A&B) path is shortened, shorter data paths mean lesser delays, lower energy required to push the data out (you need less petrol when driving on shorter route, isn't it?!) and hence this reflects on the bandwidth increase and reduction in power dissipation.

What Arastu has to offer

We, at Arastu, have designed our IP in tight coupling with the latest industry standard and adhering to the current market trend using unique verification techniques. The IP solution that is implemented as per JEDEC standard JESD209-4A specifications includes the following,

- Verilog based Synthesizable Multi-channel LPDDR4 DRAM Memory Controller that supports all the key features including various power saving combinations, selective power down for unused DRAM channel(s), different addressing schemes, security, driver, frequency ratios (1:1,1:2,1:4) and many more

Arastu also offers Verification components,

- SystemC based LPDDR4 DRAM Memory and DFI4.0 PHY Model that are readily available for usage to Software Developers and also provides per channel transaction tracker to facilitate faster debug

- SystemVerilog based DRAM Bus Monitor and Predictor that predicts the DRAM bus utilization based upon a scheduling algorithm. The same algorithm also helps in stepping up the bus performance significantly. Monitor performs timing and protocol checks. It can also generate coverage report based on in-built functional cover points as per JEDEC specification

Using DFI from our PHY partner or DFI4.0 complaint PHY from other vendor, we can make the IP solution a complete one. Customer could choose to utilize one or more of the IP components enlisted above, depending on the requirement.

Summary

Abiding by the consumer demands, it is the need of the hour to adopt LPDDR4 memory for most compute intensive, low power requiring and high resolution display based gadgets such as smart phones, tablets and the ones pertaining to the automobile applications (Infotainment and driver assistance systems), to name a few. LPDDR4 is quickly climbing up the popularity charts owing to the benefits it has to offer in comparison to its predecessors.

At Arastu, we have been striving towards, making the integration of LPDDR4 Products into your SOC a smooth one. Our set of IPs can be utilized to reduce the time to market for gadgets that incorporate the LPDDR4 Memory. For purchasing the entire IP solution or its subset, please reach us at, marcom@arastusystems.com

About the author:

Umesh is the Founder and CEO of Arastu Systems, a company that specializes in providing IP products & related services. Umesh is a well-grounded person and likes to take a bird’s-eye view of any situation, be it engineering, people or society; then turn aside to reason in before weighing in too soon on right or wrong. With more than 20 years of experience, Umesh has contributed to many semiconductor start-ups where he engineered and managed various semiconductor SOC/EDA and ASIC/FPGA product development.

Umesh is the Founder and CEO of Arastu Systems, a company that specializes in providing IP products & related services. Umesh is a well-grounded person and likes to take a bird’s-eye view of any situation, be it engineering, people or society; then turn aside to reason in before weighing in too soon on right or wrong. With more than 20 years of experience, Umesh has contributed to many semiconductor start-ups where he engineered and managed various semiconductor SOC/EDA and ASIC/FPGA product development.

Related Semiconductor IP

- DDR4 & LPDDR4 COMBO IO for memory controller PHY, 3200Mbps on TSMC 22nm

- LPDDR4X / LPDDR4 Controller

- Simulation VIP for LPDDR4

- LPDDR4 Synthesizable Transactor

- LPDDR4 DFI Synthesizable Transactor

Related Articles

- RISC-V in 2025: Progress, Challenges,and What’s Next for Automotive & OpenHardware

- Automatically Retargeting Hardware and Code Generation for RISC-V Custom Instructions

- Veri-Sure: A Contract-Aware Multi-Agent Framework with Temporal Tracing and Formal Verification for Correct RTL Code Generation

- Retargeting IP -> Effective designs eye next generation

Latest Articles

- A Lightweight High-Throughput Collective-Capable NoC for Large-Scale ML Accelerators

- Quantifying Uncertainty in FMEDA Safety Metrics: An Error Propagation Approach for Enhanced ASIC Verification

- SoK: From Silicon to Netlist and Beyond Two Decades of Hardware Reverse Engineering Research

- An FPGA-Based SoC Architecture with a RISC-V Controller for Energy-Efficient Temporal-Coding Spiking Neural Networks

- Enabling RISC-V Vector Code Generation in MLIR through Custom xDSL Lowerings