eUSB2V2 with 4.8Gbps and Use Cases: A Comprehensive Overview

By David Shin, Cadence

When developing system-on-chip (SoC) solutions, the key features often minimize size, maximize performance, and achieve low power consumption while decreasing costs. These requirements are true for most industries, including AI-powered consumer devices, energy-intensive data centers, cloud-based enterprise systems, and smart autonomous vehicles. To meet these stringent requirements, selecting the right interface IP under advanced-process nodes became a crucial part of the development, especially for those at 5nm or smaller technology nodes. Of the various interface IP available, the USB interface has become a staple for nearly all SoCs. The introduction of embedded USB 2.0 (eUSB2) by the USB Implementers Forum (USB-IF) in 2018 addressed the challenges of supporting lower I/O voltages required by these advanced-process nodes.

After eUSB2 was introduced, it was successfully positioned in the market for low-voltage SoCs and paired devices as an alternative to USB 2.0, supporting the data rate at up to 480Mbps. However, as technology advances, simply sticking with eUSB2 is not enough. The market demands higher data rates, lower power consumption, and enhanced resilience to EMI noise. To meet these demands, an upgraded version has been introduced.

On September 27, 2024, a significant update, “Embedded USB2 Version 2.0: Supplement to the USB 2.0 Specification,” commonly referred to as eUSB2V2, was released. This specification introduces several key enhancements over the previous eUSB2 standard.

eUSB2V2 scales up to 4.8Gbps of data rate and provides the flexibility to configure either asymmetrical or symmetrical links to build an efficient system, depending on the intended application. In asymmetrical link mode, one direction can achieve speeds of up to 4.8Gbps, while the reverse direction can operate at a lower rate of 480Mbps. This flexibility allows for simpler designs, optimized power consumption, and reduced EMI noise. Symmetrical links, on the other hand, can be configured to run at speeds between 960Mbps and 4.8Gbps.

eUSB2V2 has a few new features. It links with the new UTMI standard, UTMI 2.0, and supports native mode only. Unlike the original eUSB2, where the PHY could interface with an existing USB 2.0 controller, eUSB2V2 requires a dedicated controller for operation. Notably, the eUSB2V2 specification does not require backward compatibility with eUSB2v1. Optional support of symmetric 480Mbps operation can be enabled in eUSB2v1’s native mode.

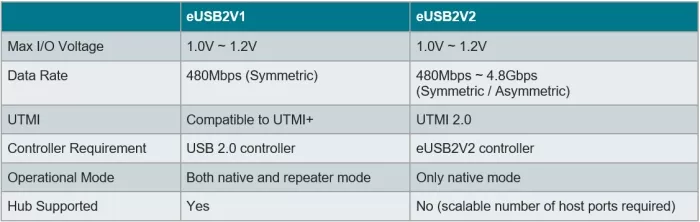

This table highlights the difference between eUSB2V1 and eUSB2V2.

This diagram explains how eUSB2v1 and eUSB2v2 operate in both native and repeater modes.

To understand better the potential impact of eUSB2V2, let’s explore some typical use cases where this upgraded standard can shine.

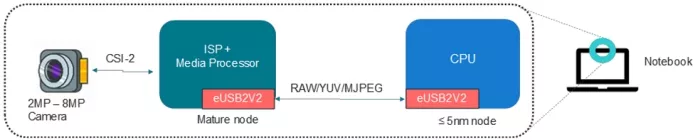

Modern notebook PCs are commonly equipped with at least one camera or two, including world-facing and face-detect IR cameras that typically feature 1080p (FHD) and VGA resolution. As with newer high-end notebook PCs, there is a growing demand for higher resolution, with 2K ~ 4K (UHD) cameras increasingly becoming standard. However, more than the 480Mbps data rate of USB 2.0 or eUSB2V1 is needed to support the higher bandwidth requirements of such high-resolution camera systems. A faster interface is required to handle the USB connection between the main SoC and the cameras (to be exact, an image signal processor (ISP) connected to the cameras through a CSI-2 interface). eUSB2V2, with its 4.8Gbps data rate and lower power consumption, offers a solution that avoids the complexity and inefficiency of the symmetrical link of adapting USB 3.x while meeting these demands.

In addition to camera applications in notebook PCs, eUSB2V2 can be used in many other scenarios. It can connect AI-enabled IoT devices and wireless communication modules to main SoCs, providing fast data transfer, simple integration, and low EMI noise. The result is a powerful, efficient solution for modern SoC designs across a wide array of applications.

eUSB2V2 offers great flexibility for modern technology and applications by delivering a high data rate, flexible link configuration, minimized EMI noise, and low power consumption. Especially for SoCs at advanced-process nodes (5nm or smaller) and devices with mature process nodes to connect the SoCs, the new eUSB2V2 standard is becoming the go-to USB interface to consider, complementing the ubiquitous USB philosophy.

Cadence has been a leading USB IP provider and recently added end-to-end eUSB2V2 solutions to its complete USB product portfolio. This includes the eUSB2V2 host and peripheral controllers, PHYs, drivers, and VIP. Learn more at Cadence.com

Related Semiconductor IP

- embedded-USB2 (eUSB2) Repeater

- eUSB2 Repeater

- eUSB2 v1.2 Dual-Role, repeater/native mode PHY, TSMC N3P, 1.2V, N/S orientation

- eUSB2 v2 Verification IP

- eUSB2 v1 Verification IP

Related White Papers

Latest White Papers

- Ramping Up Open-Source RISC-V Cores: Assessing the Energy Efficiency of Superscalar, Out-of-Order Execution

- Transition Fixes in 3nm Multi-Voltage SoC Design

- CXL Topology-Aware and Expander-Driven Prefetching: Unlocking SSD Performance

- Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

- Automating NoC Design to Tackle Rising SoC Complexity