Logic Design Solutions Announces Gen 5 NVMe Host IP on AGILEX 7 R-Tile

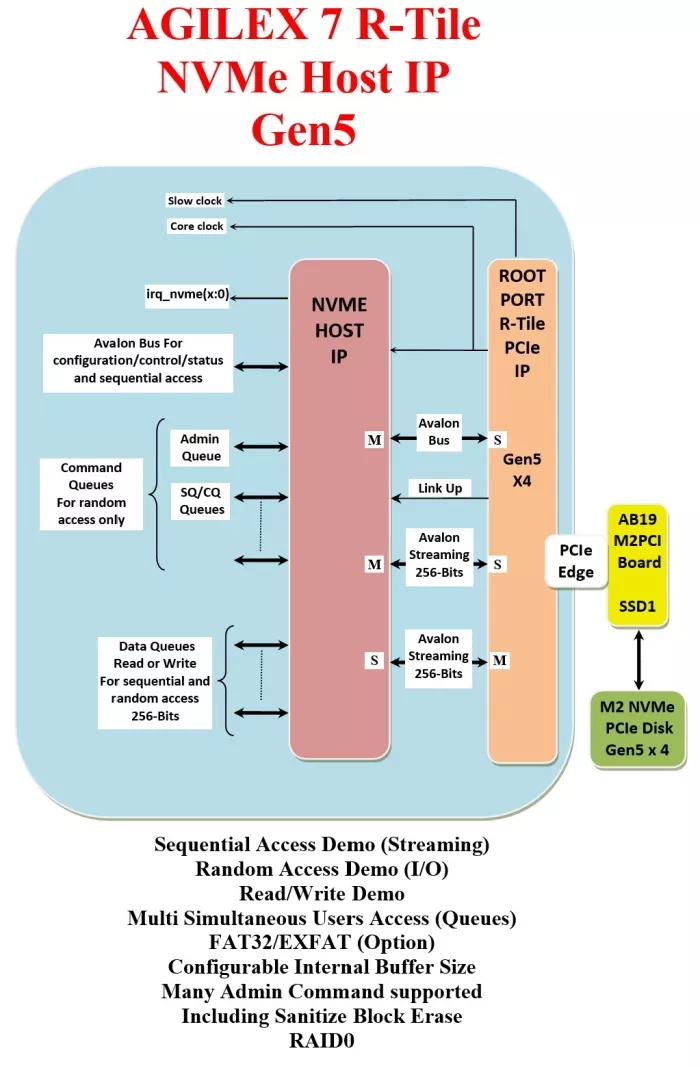

France, Gournay sur Marne, September 8 2025 – The Gen5 NVME-HOST-IP on AGILEX 7 R-Tile of Logic Design Solutions is now available. It enables random access, sequential access, Read/Write access and multi-user access. FAT32/EXFAT file system working in RAID0 is available as an option.

To show these features, several demos, from which customers can re-use to start their project, are ready to use :

- Sequential access on one disk, two disks or four disks with or without FAT32/EXFAT.

- Random access evaluation.

- Simultaneous write access and read access on one disk, two disks or four disks .

- CPU (C Source code provided) or State Machine (VHDL provided) Demo.

All of these features in one single IP at PCIe Gen5 speed.

No need anymore to buy separate IP for each function.

Related Semiconductor IP

- AGILEX 7 R-Tile Gen5 NVMe Host IP

- NVMe 2.2 Verification IP

- NVMe Streamer

- NVME Host Zynq IP

- NVME Host Kintex IP

Related News

- Logic Design Solutions launches a new version of its NVMe HOST IP Targeting embedded recorder systems

- Logic Design Solutions launches an EXFAT IP Soft Core for NVMe Host

- Logic Design Solutions Introduces the first member of NVMe HOST RECORDER IPs

- Logic Design Solutions Introduces the first NVMe Host IP on PolarFire FPGA

Latest News

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025

- Omnitrx introduces Omni500 Ethernet Evaluation Platform, Built on Comcores Expertise

- Three Misconceptions About the $402B Semiconductor Foundry Industry