Intento Design announces the launch of ID-Calibre, an ID-Substrate extension for behavioural TCAD simulation on a complete AMS chip

Paris, July 30, 2020: Intento Design, a rising EDA startup founded in 2015, provides innovative AI-based tools for analog design acceleration. Born from 25 years of research, the company aims to revolutionize traditional analog design methodology, enabling our customers to produce first-time-right AMS chips in a significantly shorter time.

After the launch of ID-Substrate, a reliability tool for early detection and prevention of all substrate parasitics, Intento Design presents ID-Calibre, an AI-based calibration tool (full release before the end of 2020). While ID-Substrate models a substrate of a complete chip as an active 3D physical model in just a few seconds, ID-Calibre calibrates the extracted substrate model for any foundry design kit, melding AI/ML with semiconductor physics. This addition answers the industry need for fast and accurate early failure prediction, critical in automotive/aerospace, as well as power management, medical, and defence applications.

Ramy Iskander, CEO & founder of Intento Design, clarifies how ID-Calibre opens new market opportunities, “ID-Calibre eliminates the need for empirical calibration or test structure fabrication, effectively bringing better market competitiveness and increased ROI to IDMs, fabless, and design houses.”

Iskander adds, “Think of ID-Substrate/ID-Calibre as a behavioural TCAD simulation of a complete AMS chip 1000x faster than traditional TCAD finite element methods”.

The introduction of ID-Calibre will further accelerate accurate prediction of all potential substrate failure areas detected by IDSubstrate, while also eliminating test structure fabrication and foundry measurement expenses.

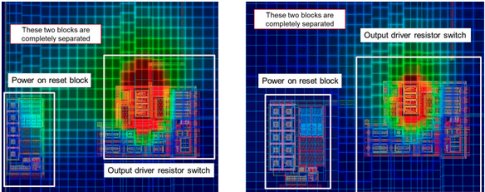

The images below illustrate how ID-Substrate/ID-Calibre set predicts substrate failures and guides layout adjustment before tape-out and fabrication. A power-on-reset signal is systematically generated when the chip is powered on. ID-Substrate analysis detected the problem area and layout adjustment was performed to protect the POR block from minority carriers induced by the output driver resistor switch. The extraction time was 1.606 seconds for a total of 2016 diodes, 8283 resistors, and 3309 homojunctions.

PowerOnReset Signal Generator: Left – minority carrier propagation detected, Right – correction made by layout adjustment.

All actors of the semiconductor ecosystem, from foundries to design houses, can profit from ID-Substrate/ID-Calibre to immunize their chips against substrate failures, thus boosting their ROI and shortening time-to-market.

Related Semiconductor IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

Related News

- Analyst: Slowdown seen in fab tool biz

- Lattice Announces Update to ispLEVER FPGA Design Tool Suite

- Altera Launches Embedded Initiative with New System Level Integration Tool for Embedded Systems Configurability

- ASSET's ScanWorks is first development tool for the emerging IJTAG embedded instrumentation standard

Latest News

- Analog Bits Demonstrates Real-Time On-Chip Power Sensing and Delivery on TSMC N2P Process at TSMC 2026 Technology Symposiums

- TES offers a High-Frequency Synthesizer and Clock Generator IP for X-FAB XT018 - 0.18µm BCD-on-SOI technology

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025