GOWIN Semiconductor & Andes Technology Corp. Announce The First Ever RISC-V CPU and Subsystem Embedded 22nm SoC FPGA

GOWIN Is Offering the Andes A25 RISC-V CPU IP and AE350 Subsystem As Instantiated Hard Cores in Its GW5AST-138 FPGA

San Jose, August 29, 2023 - Andes Technology Corporation (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099), a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of RISC-V International, is thrilled to announce that its AndesCore™ A25 RISC-V CPU IP and AE350 peripheral subsystem is hardened and embedded in the GW5AST-138 FPGA chip from GOWIN Semiconductor, the world’s fastest growing FPGA company. This integration, one of the first complete RISC-V microcontrollers in an FPGA, provides designers the A25 processor power and the peripherals most processors require without consuming any FPGA resources. Thus, the hardware team can populate the FPGA with their value-added design while the software team can concurrently create application code based on the rich RISC-V ecosystem.

“Andes is committed to delivering cutting-edge RISC-V technologies allowing developers to create innovative and efficient solutions. The integration of the A25 RISC-V CPU and AE350 peripheral subsystem as a hard core in GOWIN Semiconductor’s GW5AST-138 FPGA marks a significant milestone in achieving this vision,” said Andes North America VP of Sales, Vivien Lin. “This represents a significant milestone for the RISC-V architecture as it provides our joint customers a versatile hardware development platform to create, debug, and verify their ultimate SoC design before committing their netlist for silicon fabrication. For customers not requiring an SoC, it will enable a complete RISC-V computer ready to drive their end applications.”

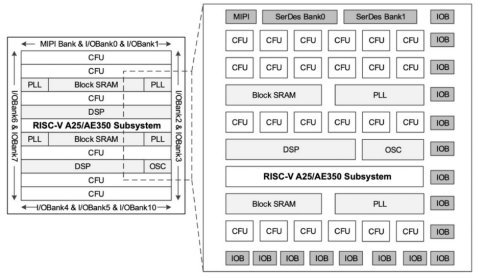

"In the Arora V family, we incorporate the peripherals that a RISC-V CPU typically requires in hard instantiations," says GOWIN’s Sr. Director of Solution Development, Jim Gao. “We included a fully controllable high-speed SerDes for communication, video aggregation, and AI computing acceleration applications that demand very high data rates. Other instantiated functions include Block RAM modules supporting ECC error correction, high-performance multiple voltage GPIO, and high accuracy clock architecture. These hard functions save the FPGA programmable fabric of up 138K LUT’s for the designers’ unique logic implementation."

About the RISC-V Based GW5AST-138 FPGA:

The AndesCore™ A25 hard core, running at 400MHz, supports the RISC-V P-extension DSP/SIMD ISA (draft), single- and double-precision floating point and bit-manipulation instructions, and MMU for Linux based applications. The AE350 AXI/AHB-based platform comes with level-one memories, interrupt controller, debug module, AXI and AHB Bus Matrix Controller, AXI-to-AHB Bridge and a collection of fundamental AHB/APB bus IP components pre-integrated together as a system design. DDR3 controller and SPI-Flash controller in the FPGA fabric back up the A25's 32KByte I-Cache and D-Cache after cache misses. Off chip DDR3 provides data memory, SPI-Flash contains the A25's instruction memory (codes copied from SPI-Flash into DDR3 and Cache upon boot-up). Besides hard instantiated functions, the GOWIN GW5AST-138 FPGA fabric affords 138K LUTs for custom design implementation. GOWIN EDA provides an easy-to-use FPGA hardware development environment for the Arora V. The environment supports multiple RTL-based programming languages, synthesis, placement and routing, bitstream generation and download, power analysis and in-device logic analyzer.

Price & Availability

The GW5AST-138 FPGA with SDK with GOWIN_V1.9.9 Beta-3 will be available August 18 through distribution.

About GOWIN Semiconductor Corp.

Founded in 2014, GOWIN Semiconductor Corp., headquartered with major R&D in China, has the vision to accelerate customer innovation worldwide with our programmable solutions. We focus on optimizing our products and removing barriers for customers using programmable logic devices. Our commitment to technology and quality enables customers to reduce the total cost of ownership from using FPGA on their production boards. Our offerings include a broad portfolio of programmable logic devices, design software, intellectual property (IP) cores, reference designs, and development kits. We strive to serve customers in the consumer, industrial, communication, medical, and automotive markets worldwide.

For more information about GOWIN, please visit www.gowinsemi.com

About Andes Technology

Eighteen years in business and a Founding Premier member of RISC-V International, Andes is a publicly listed company (TWSE: 6533; SIN: US03420C2089; ISIN: US03420C1099), a leading supplier of high-performance/ low-power 32/64-bit embedded processor IP solutions, and the driving force in taking RISC-V mainstream. Its V5 RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit Out-of-Order processors with DSP, FPU, Vector, Linux, superscalar, and/or multi/many-core capabilities. By the end of 2022, the cumulative volume of Andes-Embedded™ SoCs has surpassed 12 billion.

For more information, please visit https://www.andestech.com

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- GOWIN Semiconductor New 22nm High-Performance FPGA family - Arora V

- Microchip's Low-Cost PolarFire® SoC Discovery Kit Makes RISC-V and FPGA Design More Accessible for a Wider Range of Embedded Engineers

- Primemas Selects Achronix Embedded FPGA Technology For System-on-Chip (SoC) Hub Chiplet Platform

- S2C and Andes Technology Announce FPGA-Based Prototyping Partnership to Accelerate Advanced RISC-V SoC Development

Latest News

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025

- Omnitrx introduces Omni500 Ethernet Evaluation Platform, Built on Comcores Expertise

- Three Misconceptions About the $402B Semiconductor Foundry Industry