eSilicon, Samtec and Wild River Technology Offer High-Performance Communications Webinar

Technology and collaboration required to deliver high-performance communciations will be presented

SAN JOSE, Calif. — June 20, 2019— eSilicon, Samtec and Wild River Techology will collaborate to present a webinar that details what is required to deliver high-performance communications. Entitled High-Performance Communications, Delivered, the webinar will be held on July 11, 2019 and will be offered at two times. An introduction and webinar moderation will be provided by SemiWiki. Details of the webinar and registration are available here.

Exploding data volumes are creating the need for faster data communications. Delivering this capability has two challenges — working silicon that can deliver the required performance and a test fixture that allows system designers to verify performance in their target application. In this webinar, we’ll discuss both challenges. Technology, methodology and strong collaboration all play a part.

Our discussion will focus on PAM4 (pulse amplitude modulation) systems operating at 56 gigabits per second and beyond. PAM4 is a modulation technique whereby four distinct pulse amplitudes are used to convey the information.

Topics covered in the webinar include:

- An introduction to the challenges of high-performance communications from SemiWiki

- An overview of the test fixture design, presented by Wild River Technology

- A discussion of connectivity requirements for these systems presented by Samtec

- The process of bringing it all together — high-performance SerDes and test fixture, presented by eSilicon

All attendees will also receive a new white paper entitled:

Meeting the demands of PAM4 systems at 56Gbps and beyond

Technology, a winning methodology and the desire to collaborate all matter

Webinar registration is available here.

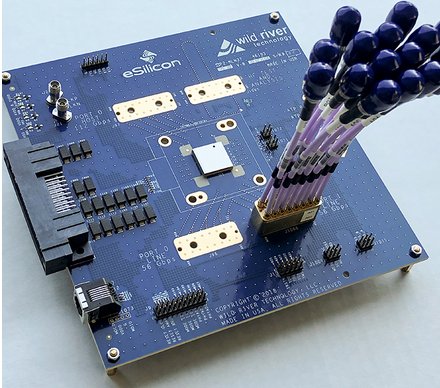

Advanced SerDes test system developed by eSilicon, Wild River Technology and Samtec.

About Wild River Technology

Wild River Technology markets products for the high-speed Signal Integrity Practitioner – an individual who addresses challenges in modeling interconnects, making better measurements, and solving a plethora of signal integrity issues to 32Gbpsec data rates.The objective of our Channel Modeling Platforms, Adapter and Cable Products, and Measurement Workspace product lines is to elevate SI practices and methodology. For more information, please visit wildrivertech.com.

About Samtec

Founded in 1976, Samtec is a privately held, $800MM global manufacturer of a broad line of electronic interconnect solutions, including High-Speed Board-to-Board, High-Speed Cables, Mid-Board and Panel Optics, Precision RF, Flexible Stacking, and Micro/Rugged components and cables. With 40 locations in 18 different countries, Samtec’s global presence enables its unmatched customer service. For more information, please visit www.samtec.com.

About eSilicon

eSilicon provides complex FinFET ASICs, market-specific IP platforms and advanced 2.5D packaging solutions. Our ASIC-proven, differentiating IP includes highly configurable 7nm 56G/112G SerDes plus networking-optimized 16/14/7nm FinFET IP platforms featuring HBM2 PHY, TCAM, specialized memory compilers and I/O libraries. Our neuASIC platform provides AI-specific IP and a modular design methodology to create adaptable, highly efficient AI ASICs. eSilicon serves the high-bandwidth networking, high-performance computing, AI and 5G infrastructure markets. www.esilicon.com

Related Semiconductor IP

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

Related News

- eSilicon and Wild River Technology Announce Advanced SerDes Test System

- SK Hynix, Amkor Technology, eSilicon, Northwest Logic and Avery Design Systems Announce "Start your HBM/2.5D Design Today" Webinar

- DesignCon 2019: eSilicon to demonstrate 7nm 56G DSP SerDes over 5-meter Samtec cable assembly

- OFC 2019: eSilicon to demonstrate two 7nm IP products, 56G DSP SerDes over a 5-meter Samtec cable assembly and a complete HBM2 PHY subsystem

Latest News

- Analog Bits Demonstrates Real-Time On-Chip Power Sensing and Delivery on TSMC N2P Process at TSMC 2026 Technology Symposiums

- TES offers a High-Frequency Synthesizer and Clock Generator IP for X-FAB XT018 - 0.18µm BCD-on-SOI technology

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025