Dolphin Design unveil a new and improved version of its Power Controller IP - MAESTRO - to speed-up energy-efficient SoC design

Dolphin Design unveil a new and improved version of its Power Controller IP - MAESTRO - to speed-up energy-efficient SoC design

Grenoble, France – December 7, 2020 -- With the growing chip complexity observed in many market segments, in addition to a need for longer battery life, SoC design teams are forced to adopt advanced power management techniques to improve the energy-efficiency of their devices. Recent process nodes offer a high level of SoC integration with RF connectivity, logic MCU, non-volatile memory, AI/ML processor and analog blocks on the same die, so system and power architects now have to deal with:

- Fast wake-up times to ensure instant-on operation from sleep and stand-by modes

- Control of multiple voltages on the same die to supply MCU/logic, RF, analog and SRAM domains

- Fine-grain control of power and clock gating to instantaneously switch-on / switch-off domains

- Increasing number of power modes for maximum flexibility at application-level

- Fast transitions during power mode changes to minimize energy consumption

The conventional approach for PMU design is to use a software-based solution to control the devices involved in power management. Software brings a highly flexible and configurable alternative for PMU implementation, however it requires an always-active CPU to manage the power schemes, with the penalty of hundreds of power-consuming CPU clock cycles and accesses to Flash memory.

Another approach used by design teams with more experience in power management, is to adopt hardware solutions to enable low-latency control of their power devices with decreased power consumption. However, designing full custom logic for power control requires an in-depth expertise in power management and drastically increases the design and verification cycle time. In addition, a full-custom PMU tailored for a given circuit is hardly portable and scalable to another product, even for low or mid-complexity SoC.

The ideal solution would mix the configurability of a software PMU together with the lowest power consumption of a hardware PMU.

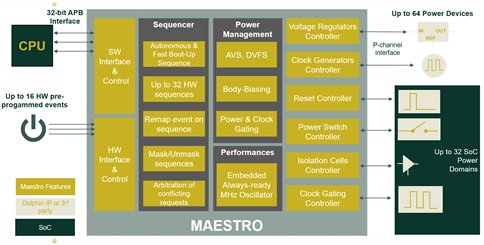

Dolphin Design make this possible with its latest version of MAESTRO, a unique Power Controller RTL IP which is now accompanied by PowerStudio compiler to speed-up the design of a highly scalable power controller that features breakthrough capabilities compared to traditional HW or SW PMU design methodologies.

MAESTRO features:

- Dual operation mode

- CPU-less HW operation mode for low-power and low latency control of power devices

- Flexible SW operation mode with a standard 32-bit APB interface that enables on-the-fly execution of SW-based power sequences

- Embedded sequencer for autonomous control of power mode transitions, including boot-up and wake-up sequences where CPU is off

- Event-based architecture to trigger any power sequence (up to 16 pre-programmed HW events)

- Built-in always-ready 10 MHz oscillator to enable fast wake-up when RTC clocks are shutdown

- Fine-grain control of power devices (regulators, clock generators) with standard p-channel interface, enabling smooth support of both IP from Dolphin Design or 3rd party provider

MAESTRO is now augmented with PowerStudio compiler to enable a faster path from architecture to integration, featuring:

- Power State Table and Power Mode Changes GUI for fast configuration: design in a single day, iterate in a single hour

- MAESTRO gate count & transition time calculator

- Automated generation of MAESTRO RTL configuration

- Automated generation of UPF test-bench for PMU in-context verification

MAESTRO is currently being used to enable multiple customer tape-outs in various silicon technology nodes, including FD-SOI and bulk technologies.

Design an energy efficient power management system in days, not months. Do more, with less energy.

Adopt MAESTRO.

About Dolphin Design

Headquartered in France, Dolphin Design, previously known as Dolphin Integration, is a semiconductor company employing 160 people, including 140 highly qualified engineers.

They provide differentiating platform solutions built on state-of-the-art IPs and architectures, customized by unique system level utilities to deliver fast and secure ASICs, either designed by or for their clients. These platforms are available for various technological processes and optimized for Energy Efficient SoC Design.

Alongside their clients, now exceeding 500 companies, they focus on human, inventive and long-term collaboration to enable them to bring products, powered by innovative and accessible integrated circuits that minimize environmental impact, to the hands of billions of people everyday. In consumer markets including IoT, AI and 5G, and in high reliability markets, they unleash SoC designer creativity to deliver differentiation.

Tell them your biggest dream. Dare the impossible. They tech it on.

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- MIPI CSI-2 CSE2 Security Module

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

Related News

- SigmaSense Teams Up with Dolphin Design to Deliver Power Efficiency in their Advanced SDC300 Touch Controller

- CAST Introduces Microsecond Channel Controller IP Core for Automotive Power and Sensor Interfaces

- DI3CM-HCI, A High-Performance MIPI I3C Host Controller IP Core for Next-Generation Embedded Designs

- Perceptia Devices and Dolphin Semiconductor Partner to Deliver Best-in-Class IP Portfolio Covering Power Management, Clocking, High-Quality Audio and In-Situ Monitoring

Latest News

- Arasan acheives the Industry's First ASIL-D Certification for its CAN XL IP Core

- Quintauris and Elektrobit Partner to Enable Reliable RISC-V Solutions for Automotive

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems