Codasip Announces FPGA Evaluation Platforms for RISC-V Processor Cores

Munich, Germany – April 21st, 2021 – Codasip, the leading supplier of processor design solutions and RISC-V processor IP, announces two new FPGA Evaluation Platforms for accelerated evaluation of Codasip RISC-V IP. The Platforms are designed to target Digilent boards based on Xilinx Artix-7 and Kintex-7 FPGAs.

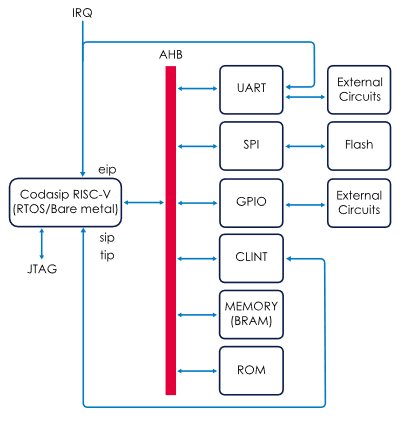

The Codasip Evaluation Platforms contain the selected RISC-V processor IP core with a subsystem containing peripherals and AMBA interconnect. A testbench layer includes a clock generator and block RAMs for internal memories, and can use some of the FPGA peripherals such as flash memory. Additionally, customers will receive a Vivado project and bitmap files for their target FPGA board. The platforms include an SDK, the CodeSpace IDE, software examples, and a Get Started Guide and documentation on how to use the peripherals.

“The new platforms will greatly simplify evaluation of Codasip Embedded and Application cores using Xilinx FPGAs, allowing customers to get started in a matter of minutes”, says Dr Zdeněk Přikryl, CTO Codasip. “We aim to provide a comfortable evaluation experience over the range from simple embedded cores to multi-core application processor systems.”

The Codasip Embedded Processor Evaluation Platform based on AHB is suitable for low power and high performance embedded cores such as the Codasip L30, L50, H50 and H50X. It can be used for evaluating systems with either bare metal software or RTOS (e.g. FreeRTOS). The bitmap files target the cost effective Digilent Nexys A7.

Codasip FPGA Evaluation Platform for Embedded Cores

The Application Processor Evaluation Platform, using either AHB or AXI, aims to support single- or multi-core systems using application processors such as the A70X. The platform comes with flash images for embedded Linux and documentation to explain compilation of Linux and user applications. For a simple single-core A70X, the Digilent Nexys A7 can be targeted. For multi-core systems, the more complex Digilent Nexys Video (MP1 or MP2) and Digilent Genesys 2 (MP4) boards are required.

Codasip FPGA Evaluation Platform for Application Cores

Related Semiconductor IP

- Compact Embedded RISC-V Processor

- Highly configurable HW PQC acceleration with RISC-V processor for full CPU offload

- Vector-Capable Embedded RISC-V Processor

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

- Enhanced-Processing Embedded RISC-V Processor

Related News

- Codasip looks to Silicon Creations’ PLL to drive RISC-V Automotive Safety-Critical Core

- Breker Verification Systems and Frontgrade Gaisler Collaborate on High-Reliability RISC-V Fault-Tolerant Processor Core

- Bluespec, Inc. Releases Ultra-Low Footprint RISC-V Processor Family for Xilinx FPGAs, Offers Free Quick-Start Evaluation.

- Blueshift Memory to use Codasip custom compute to develop new memory-efficient processor technology

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud