Codasip launches complete exploration platform to accelerate CHERI adoption

Codasip Prime comprises pre-silicon hardware and software development kits to realize state-of-the-art memory-safe compute

Munich, Germany – April 29, 2025 – Codasip, the European RISC-V leader, has made available an exploration platform based on the Codasip X730 application core, which integrates CHERI (Capability Hardware Enhanced RISC Instructions).

Based on commercially available IP, Codasip Prime enables advanced development of memory-safe and secure software. The platform enables hardware and software engineers to evaluate and demonstrate the capabilities of CHERI technology, develop and run CHERI software, and integrate CHERI hardware into wider test systems.

Codasip Prime features a high-performance FPGA (field programmable gate array) system, including the processor and peripherals, and a full software development kit:

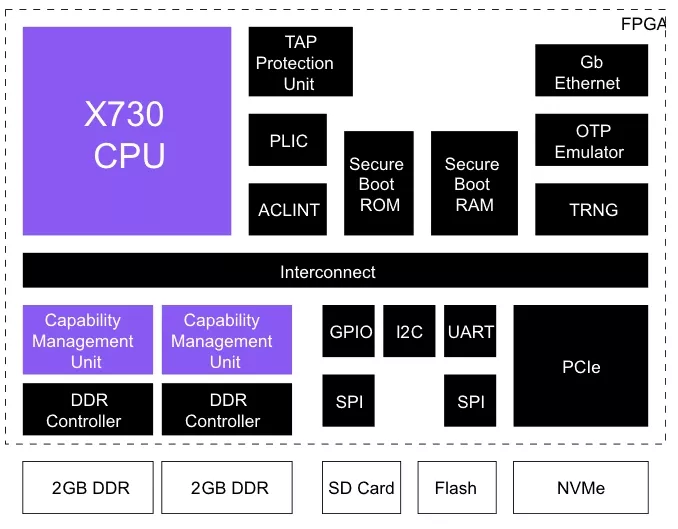

- FPGA board and bitstream containing:

- Codasip X730 64bit RISC-V CHERI Application CPU

- Peripheral and system IP

- Security IP for secure boot and secure debug (True Random Number Generator, Test Access Port Protection Unit)

- CHERI-specific IP (capability tag management for DDR memory)

- Out-of-the-box Linux demonstration image

- Debug probe

- CHERI Software Development Kit

- CHERI Linux

- CHERI C/C++ tool chain including compiler and debugger

- Secure Boot

- QEMU virtual platform matching FPGA

“Our new platform is a game changer for consumer, automotive and defense companies alike looking at adopting CHERI,” said Jamie Broome, chief product officer. “Codasip Prime allows software developers to develop and evaluate their applications before chips are built. In addition to hardware IP and software, we offer engineering support from our CHERI experts. Through our engagement with the CHERI Alliance and RISC-V International, we ensure that alignment with industry standards is maintained, enabling early adopters to trust that their integrations are future proof.”

CHERI effectively prevents memory safety issues

Security is rapidly growing in importance to businesses due to recent legislation such as the EU Cyber Resilience Act. Memory safety vulnerabilities are used in up to 87% of cyberattack chains according to one study. These attacks are very costly. For example, losses due to the well-known Heartbleed bug are estimated to exceed $500 million. CHERI is the most cost-effective way to protect against memory safety vulnerabilities. It is backwards compatible and allows migration to safer code, and it makes C/C++ memory safe, avoiding costly software re-writes.

Codasip is standardizing a CHERI extension for RISC-V in collaboration with other members of the CHERI Alliance, a community interest organization promoting the global adoption of CHERI security technology across the computing industry. Members of the alliance include the University of Cambridge, Google, the UK’s National Cyber Security Centre (NCSC) and the UK’s Defence Science and Technology Laboratory (Dstl).

Codasip X730 is the first commercial implementation of the new CHERI-RISC-V extension and is immediately available.

Related Semiconductor IP

- Dual-issue Linux-capable RISC-V core

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

Related News

- embedded world 2024: Codasip demonstrates CHERI memory protection

- Codasip announces strategic licensing agreement with EnSilica for its CHERI-enabled embedded CPU from the 700 family

- Sonics and CoWare Introduce Advanced Exploration Solution for Multiprocessor SoC Architectures

- CoWare and Tenison Accelerate Creation of Virtual Hardware Platforms for Architectural Exploration and Software Development

Latest News

- TSMC Chases Soaring AI Demand

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing