Codasip Announces A71X RISC-V Application Core with Dual-Issue Capability

Munich, Germany – June 22, 2021 – Codasip, the leading supplier of customizable RISC-V® processor IP, today announces a new major version of its most advanced processor IP core: the A71X™ with dual-issue support for enhanced performance.

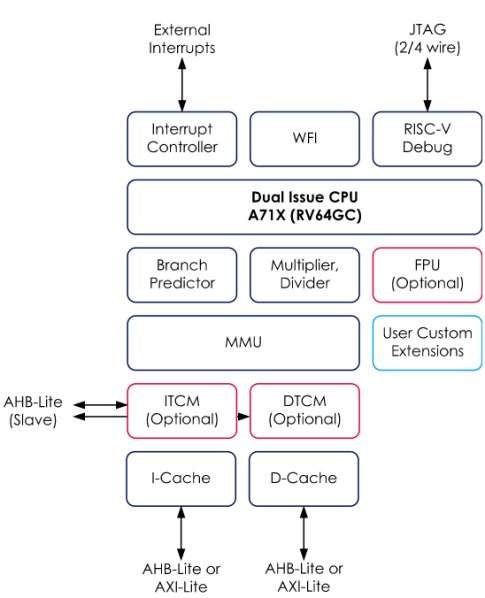

A71X is a RISC-V-based 64-bit core aimed at the application domain and able to run Linux. It is Codasip’s first superscalar core, able to process instructions from one thread in two different execution units. This feature offers greatly improved performance, up to double the performance of a single-issue core.

Dual-issue core

The configurations of A71X will include all microarchitectures that have already been announced for the earlier Codasip A70X™, including support for the RISC-V P extension and multi-core features. Together with the dual-issue capability, this will enable the design of powerful processors suitable for fast data-intensive applications in ML/AI, automotive, and similar domains.

“This is a very important addition to our application processor IP portfolio,” says Zdeněk Přikryl, CTO Codasip. “The new dual-issue capability will allow for a jump in performance without significant increase in power and area, which will make it possible to serve a much wider range of applications.”

All Codasip Application processor cores (those with code names beginning with “A”) are 64-bit and use an AHB or AXI external interface. They also feature a Floating-Point Unit and Atomic instructions. All of them can run Linux as they support Machine, Supervisor & User privilege modes and have a Memory Management Unit.

All Codasip RISC-V cores for all domains (Low-Power Embedded, High-Power Embedded, and Application) are developed using Codasip Studio and provided as easy-to-customize CodAL models.

The A71X core and its configurations will be available towards the end of 2021.

Codasip A71X core

About Codasip

Codasip delivers leading-edge RISC-V processor IP and high-level processor design tools, providing IC designers with all the advantages of the RISC-V open ISA, along with the unique ability to customize the processor IP. As a founding member of RISC-V International and a long-term supplier of LLVM and GNU-based processor solutions, Codasip is committed to open standards for embedded and application processors. Formed in 2014 and headquartered in Munich, Germany, Codasip currently has R&D centers in Europe and sales representatives worldwide. For more information about our products and services, visit www.codasip.com. For more information about RISC-V, visit www.riscv.org.

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- Codasip announces three new RISC-V Application Processor Cores providing Multi-core and SIMD capability

- Codasip: Toward Custom, Safe, Secure RISC-V Compute Cores

- Codasip Faces Sale – Pivotal Moment for EU RISC-V Sovereignty

- Codasip looks to Silicon Creations’ PLL to drive RISC-V Automotive Safety-Critical Core

Latest News

- Rebellions Collaborates with SK Telecom and Arm Targeting Sovereign AI and Telecom Infrastructure

- Sarcina Launches UCIe-A/S Packaging IP to Accelerate Chiplet Architectures

- BrainChip Unveils Radar Reference Platform to Bridge the ‘Identification Gap’ in Edge AI

- Siemens accelerates AI chip verification to trillion‑cycle scale with NVIDIA technology

- SiFive Raises $400 Million to Accelerate High-Performance RISC-V Data Center Solutions; Company Valuation Now Stands at $3.65 Billion