Arasan Announces immediate availability of its I3C Host / Device Dual Role Controller IP

Aug 29, 2024, San Jose, CA -- Arasan Chip Systems, a leading provider of semiconductor IP for mobile and automobile SoCs, today announced the immediate availability of its I3C Dual/Secondary Controller IP which now includes the I3C PHY IP.

Arasan expands its MIPI IP portfolio with the announcement of the immediate availability of its I3C Dual/Secondary Controller IP including I3C PHY compliant with MIPI I3C HCI Specification (v1.2).

The I3C PHY supports the Ternary and non Ternary modes and is available on foundry nodes from 28nm to 4nm.

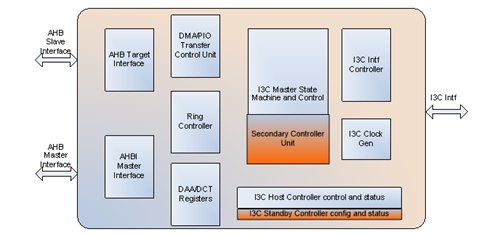

The Arasan I3C Secondary Controller IP Core implements Active controller functionality as defined by the MIPI Alliance’s I3C Specification and Secondary Controller logic. The I3C bus is used for various sensors in the mobile/automotive system where the active controller transfers data and control between itself and various sensor devices. In some applications, the active controllers can hand-off the controller role to the secondary controller on the bus. The Dual role IP joins the I3C bus as a secondary controller (as a target) and will request/accept the controller role. The IP core provides a 32bit AHB bus as an application interface to configure and control the transfers. The controller manages the control signal to IO buffers during the active and standby mode.

The I3C Dual Role controller is available for immediate licensing.

About Arasan:

Arasan Chip Systems is a leading provider of IP for mobile storage and mobile connectivity interfaces, with over a billion chips shipped with our IP. Our high-quality, silicon-proven Total IP Solutions encompass digital IP, Analog Mixed Signal PHY IP, Verification IP, HDK, and Software. With a strong focus on mobile SoCs, we have been at the forefront of the “Mobile” evolution since the mid-90s, supporting various mobile devices, including smartphones, automobiles, drones, and IoT devices, with our standards-based IP.

Related Semiconductor IP

- I3C Host Controller IP v1.2

- I3C 1.1 Host Controller

- MIPI I3C Basic v1.1.1 specifications with Host Controller Interface v1.1 specification

- I3C Controller IP – I3C / I2C Slave, Configure User Registers, no CPU Host Required

- I3C Controller IP – I3C / I2C Slave, SCL Clock only, Configure User Registers, no CPU Host Required

Related News

- DI3CM-HCI, A High-Performance MIPI I3C Host Controller IP Core for Next-Generation Embedded Designs

- Arasan to demonstrate its I3C Host and Device IP and participate at the I3C Interoperability Session at the 2018 MIPI Devcon in Seoul

- Arasan MIPI DSI-2 TX and Rx Controller achieve ISO 26262 ASIL-B Certification

- USB 4.0, USB 3.2, USB 3.1, USB 3.0, USB 2.0, Device, Hub, Host & Dual Mode proven Interface IP Controllers are available immediately to License

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud