Symmetric Encryption IP

Welcome to the ultimate Symmetric Encryption IP hub! Explore our vast directory of Symmetric Encryption IP

All offers in

Symmetric Encryption IP

Filter

Compare

171

Symmetric Encryption IP

from

43

vendors

(1

-

10)

-

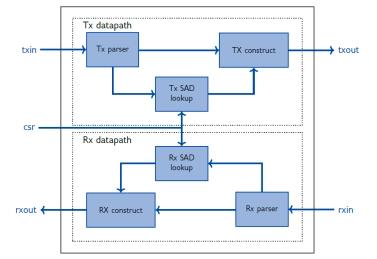

IPSEC AES-256-GCM (Standalone IPsec)

- XIP7213E implements the Internet Protocol Security (IPsec) as standardised in RFC4303 and RFC4305.

- The IPsec protocol defines a security infrastrucure for Layer 3 (as per the OSI model) traffic by assuring that a received packet has been sent by the transmitting station that claimed to send it.

-

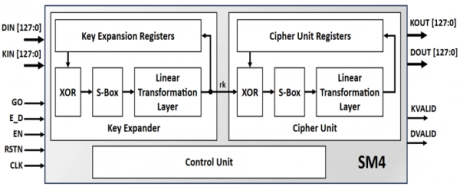

SM4 Cipher Engine

- The SM4 IP core implements a custom hardware accelerator for the SM4 symmetric block cipher, specified in Chinese national standard GB/T 32907-2016, and ISO/IEC 18033-3:2010/Amd 1:2021.

- Designed for easy integration, the core, internally expanding the 128-bit key, is capable of both encryption and decryption and features a simple handshake input and output data interface.

-

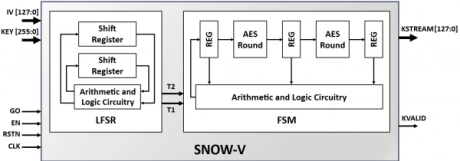

SNOW-V Stream Cipher Engine

- The SNOW-V IP core implements the SNOW-V stream cipher mechanism, aiming to meet the security demands of modern high-speed communication systems.

- It conforms to the official SNOW-V mechanism, published in 2019 by the IACR Transactions on Symmetric Cryptology, as an extensive revision of SNOW 3G stream cipher.

-

P1619 / 802.1ae (MACSec) GCM/XTS/CBC-AES Core

- Small size: From 70K ASIC gates (at throughput of 18.2 bits per clock)

- 500 MHz frequency in 90 nm process

- Easily parallelizable to achieve higher throughputs

- Completely self-contained: does not require external memory. Includes encryption, decryption, key expansion and data interface

-

AES-SX Secure Core - High-Throughput AES Core with Advanced SCA/FI Protection for Performance-Critical Systems

- The High-Performance AES IP core is a fast, silicon-proven cryptographic engine designed for systems with demanding encryption workloads.

- Built on a 20 S-box parallel architecture, it delivers exceptional AES-128/256 encryption and decryption throughput while supporting standard modes including ECB, CBC, and CTR (excluding GCM, XTS, and CBC-MAC).

-

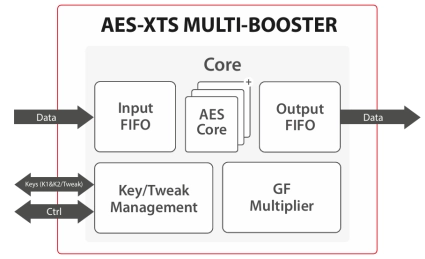

AES-XTS Multi-Booster

- The AES-XTS Multi-Booster crypto engine includes a generic & scalable implementation of the AES algorithm making the solution suitable for a wide range of low-cost & high-end applications (including key, tweak, input and output registers and Galois field multiplier).

-

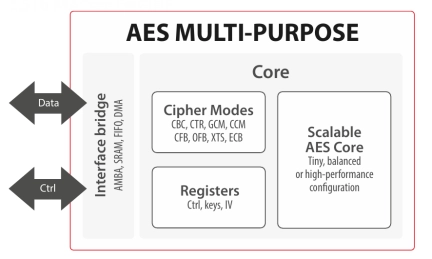

AES Mutli-Purpose crypto engine

- The AES Multi-Purpose crypto engine includes a generic and scalable implementation of the AES algorithm and a configurable wrapper making the solution suitable for a wide range of low-cost & high-end applications.

-

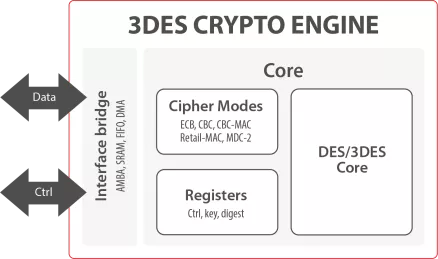

3DES Crypto Engine

- The DES/3DES crypto engine offers a hardware implementation of the Data Encryption Standard (DES) according to Federal Information Processing Standards Publication (FIPS 46-3) of the National Institute of Standards and Technology (NIST).

-

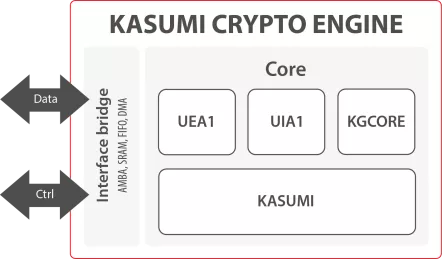

KASUMI Crypto Engine

- The KASUMI IP core is 3GPP confidentiality and integrity algorithms (UEA1/UIA1) stream cipher for telecommunication applications, requiring high performance with reduced silicon resources.

- It is optimized for maximum throughput and minimum latency.

-

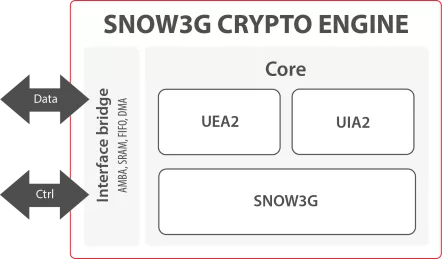

SNOW3G Crypto Engine

- ASIC and FPGA

- ETSI specifications compliant

- Supports:

- Data interface: AMBA (AXI/AHB) with optional DMA