vector processor IP

Filter

Compare

130

IP

from

36

vendors

(1

-

10)

-

-

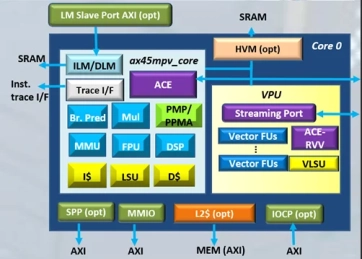

High performance dual-issue, out-of-order, 7-stage Vector processor (DSP) IP

- Design Flexibility

- Portability

- Ease of programmability

-

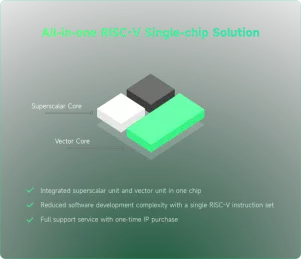

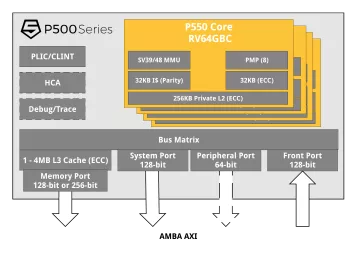

High performance Linux capable vector processor

- RV64GCV ISA with Sv39 or Sv48 support

- 8-stage dual-issue in-order pipeline with decoupled vector unit

- Machine, Supervisor, and User privilege modes

-

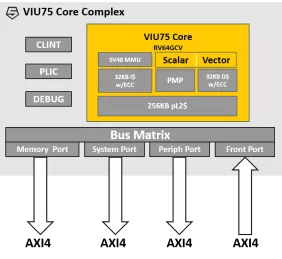

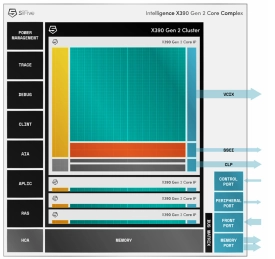

Multi-core capable RISC-V processor with vector extensions

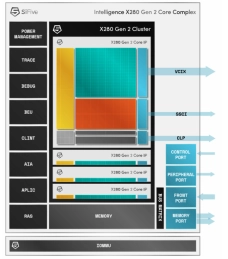

- The SiFive® Intelligence™ X280 Gen 2 is an 8-stage dual issue, in-order, superscalar design with wide vector processing (512 bit VLEN/256-bit DLEN).

- It supports RISC-V Vectors v1.0 (RVV 1.0) and SiFive Intelligence Extensions to accelerate critical AI/ML operations.

-

Highly efficient out-of-order RISC-V vector application processor series

- Full support for the RVA22 RISC-V profile specification

- Best-in-class RISC-V performance efficiency

-

High performance three-issue, out-of-order RISC-V vector application processor

- Breakthrough RISC-V performance

- Enabling next generation applications

-

8-stage dual issue, in-order, superscalar processor with dual vector processing units (1024-bit VLEN/512-bit DLEN)

- New RVA23 support

- New RVV1.0 512-bit vector engine

- New SSCI interface added alongside VCIX

- New instructions and extensions

- New improved memory subsystem

-

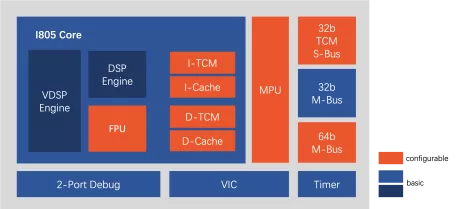

AIoT processor with vector computing engine

- Instruction set: T-Head ISA (32-bit/16-bit variable-length instruction set);

- Pipeline: 4-stage sequential pipeline;

- General register: 32 32-bit GPRs; 16 128-bit VGPRs;

- Cache: I-Cache: 8 KB/16 KB/32 KB/64 KB (size options); D-Cache: 8 KB/16 KB/32 KB/64 KB (size options);

-

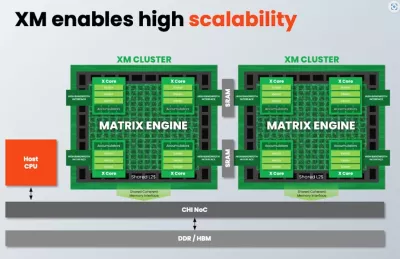

High-performance AI dataflow processor with scalable vector compute capabilities

- Matrix Engine

- 4 X-Cores per cluster

- 1 Cluster = 16 TOPS (INT8)

-

64-bit RISC-V Multicore Processor with 1024-bit Vector Extension

- 64-bit in-order dual-issue 8-stage CPU core with up to 1024-bit Vector Processing Unit (VPU)

- Symmetric multiprocessing up to 8 cores