turbo code IP

Filter

Compare

33

IP

from

12

vendors

(1

-

10)

-

High Performance Turbo Code

- Outstanding error correction performance - ideal for small/medium block sizes

- Block size: 4 bytes - 512 bytes (1-byte step)

-

High-Speed Turbo Product Code decoder

- Best use of FPGA for very high bitrate (up to 230 Mbps user bitrate at 4 iterations).

- Supports all modes of IEEE-802.16a TPCs

- Supports large block sizes (up to 65Kbits).

- Highly programmable

-

Configurable Turbo Product Codec

- Programmable data block size by adjusting codeword dimensions, i.e. number of rows and number of columns.

- Supports shortening by adjusting number of rows and columns to be eliminated in order to create a shortened code.

- Programmable number of soft bits in the input data.

- 2’s complement arithmetic data format.

-

Turbo Intel® FPGA IP

- Forward-error correction (FEC) channel codes commonly improve the energy efficiency of wireless communication systems

- Turbo codes are suitable for 3G and 4G mobile communications and satellite communications

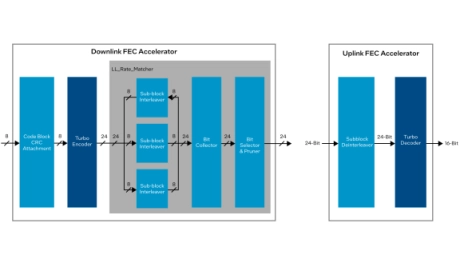

- You can use Turbo codes in other applications that require reliable information transfer over bandwidth- or latency-constrained communication links in the presence of data-corrupting noise. The 4G Turbo-V Intel® FPGA IP comprises a downlink and uplink accelerator for vRAN and includes the Turbo Intel® FPGA IP.

-

DVB-RCS2 Turbo Decoder and Encoder

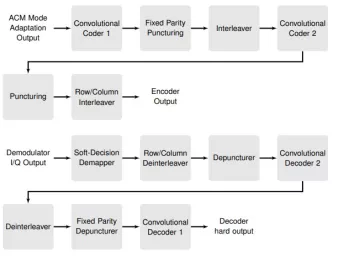

- 16-state double binary turbo Encoder/Decoder.

- Puncturing/De-puncturing on the fly.

- Run time selectable number of iterations.

- Parallel decoding algorithm.

- Hard decision output.

-

CCSDS SCCC Turbo Encoder and Decoder

- Burst-to-burst on-the-fly configuration

- High payload block length granularity (between 5,758 and 43,678 bits)

- High code rate granularity (code rates between 0.36 and 0.90)

- Configurable amount of turbo decoding iterations for trading off throughput and error correction performance

-

DVB-RCS2 turbo decoder

- Scalable throughput - up to 200 Mbits/s

- Advanced low-complexity architecture

- Selectable LLR quantization level

- On-the-fly (Block-by-block) change of configuration

-

LTE turbo decoder

- Covers rate-matching, turbo decoding and CRC decoding

- Throughput level 75 to 300 Mbps

-

4G LTE/LTE-A Turbo Decoder

- Compliant with 3GPP Release 8 LTE turbo decoding

- Compliant with 3GPP Release 10 LTE Advanced turbo decoding

- Support for codeword CRC and up to four transport block CRCs

-

High bit rate Turbo Decoder core for 3GPP LTE/ LTE A

- 3GPP LTE/ LTE A compliant

- Implements decoder for requirements as defined in Section 5.1.3.2 of the specification