turbo IP

Filter

Compare

75

IP

from

18

vendors

(1

-

10)

-

LTE Turbo Decoder

- Low power design for HW implementation

- Minimum HW cost in ASIC implementation for Turbo decoder (TDEC)

- Optimized TDEC early termination algorithms to minimize power consumption

- Fast CRC engine

-

Turbo Intel® FPGA IP

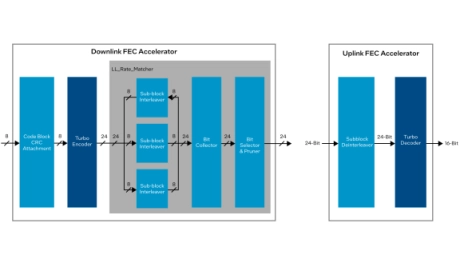

- Forward-error correction (FEC) channel codes commonly improve the energy efficiency of wireless communication systems

- Turbo codes are suitable for 3G and 4G mobile communications and satellite communications

- You can use Turbo codes in other applications that require reliable information transfer over bandwidth- or latency-constrained communication links in the presence of data-corrupting noise. The 4G Turbo-V Intel® FPGA IP comprises a downlink and uplink accelerator for vRAN and includes the Turbo Intel® FPGA IP.

-

CCSDS 131.2 SCCC Turbo Encoder and 64-APSK Modulator

- Fully synchronous design, using single clock

- Fully synthesizable drop-in module for FPGAs

- Optimized for high performance and low resources

-

CCSDS SCCC Modulator/ Turbo Encoder

- Compliant with CCSDS 131.2-B-1 Standard

- Telemetry Applications

- Supports all 27 mandatory encoding and modulation mechanisms:

- On-the-fly MODCOD block change

-

DVB-RCS2 Turbo Decoder and Encoder

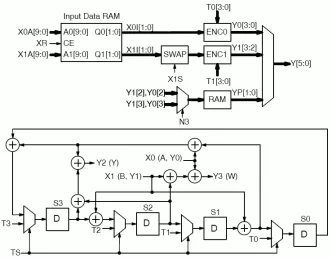

- 16-state double binary turbo Encoder/Decoder.

- Puncturing/De-puncturing on the fly.

- Run time selectable number of iterations.

- Parallel decoding algorithm.

- Hard decision output.

-

LTE Turbo Decoder

- 8-bit precision for input LLR

- 13-bit precision for internal calculations

- Provides automatic normalization for internal calculations to avoid hardware overhead

- Supports full 3GPP-LTE and UMTS block size range is supported

-

HomePlug Turbo Decoder

- Supports rates½ and 16/18 coded input.

- FEC block size support : 16, 72, 136, 264, 520 bytes

- Configurable number of Iterations

- LLR width 14 bits

-

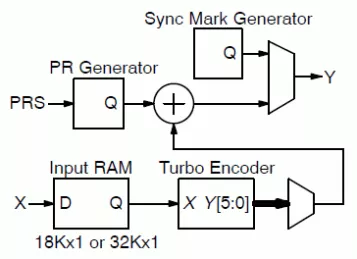

CCSDS turbo encoder with sync marker, pseudo randomiser and input memory

- 16 state CCSDS compatible turbo encoder

- Rate 1/2, 1/3, 1/4 and 1/6

- Interleaver sizes from 1784 to 16056 bits in multiples of 1784

-

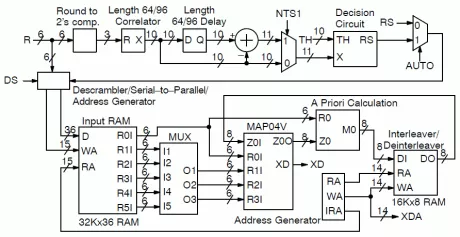

CCSDS turbo decoder with sync marker synchroniser, descrambler and input memory

- 16 state CCSDS compatible

- Rate 1/2, 1/3, 1/4 or 1/6

- Interleaver sizes from 1784 to 16056 bits

- Includes optional automatic synchronisation to non-inverted or inverted sync marker, optional descrambler and ping-pong input memory

-

16 state DVB-RCS2 Turbo Encoder

- 16 state DVB-RCS2 compatible

- Rate 1/3, 2/5, 1/2, 2/3, 3/4, 4/5, 5/6, 6/7, 7/8 with reverse output option