on-chip network IP

Filter

Compare

201

IP

from

29

vendors

(1

-

10)

-

High speed NoC (Network On-Chip) Interconnect IP

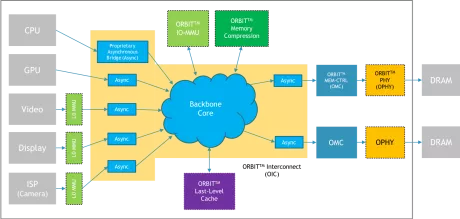

- The ORBIT On-Chip Interconnect (OIC) delivers exceptional performance, and SoC design flexibility based on automated end-to-end interconnect generation flow.

- It enables high-speed routing with pre-calculated routing path details and supports higher speed, low latency, and floorplan flexibility.

-

Network on Chip

- The Network on Chip (NOC) technology redefines typical NOC capabilities as it extends the on-chip network beyond chip(let) boundaries.

- The network is seamlessly extended across all chip(let)s forming a system.

- Customers basically can split up monolithic SOCs into a chiplet based system and still having a coherent system enabling a lean and efficient SW/FW stack while operating at full performance.

-

Run-time Reconfigurable Neural Network IP

- Customizable IP Implementation: Achieve desired performance (TOPS), size, and power for target implementation and process technology

- Optimized for Generative AI: Supports popular Generative AI models including LLMs and LVMs

- Efficient AI Compute: Achieves very high AI compute utilization, resulting in exceptional energy efficiency

- Real-Time Data Streaming: Optimized for low-latency operations with batch=1

-

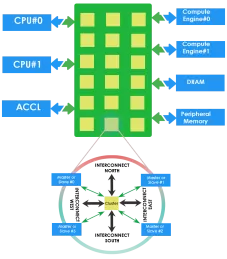

Coherent Mesh Network

- High-Performance, Scalable Coherent Mesh

- Reduce SoC Integration Time

- Maximize Compute Density

- Coherent Multichip Links

-

Power efficient, high-performance neural network hardware IP for automotive embedded solutions

- Power efficient, high-performance

- For automotive embedded solutions

-

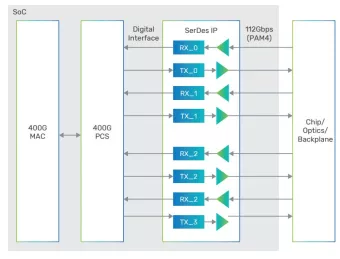

224G-LR SerDes PHY enables 1.6T and 800G networks

- Optimized Performance, Power and Area with Design Agility

- Supports full-duplex 1.25 to 225Gbps data rates

- Enables 1.6T, 800G, 400G, and 200G Ethernet with a PHY + Controller solution

- Supports evolving IEEE 802.3 and OIF-CEI-224G standard electrical specifications

- Meets the performance requirements of chip-to-module (VSR), chip-to-chip (MR), and copper/backplane (LR) interconnects

-

Coherent Network-on-chip (NoC) IP

- Layered, scalable, configurable, and physically aware configurable NoC

-

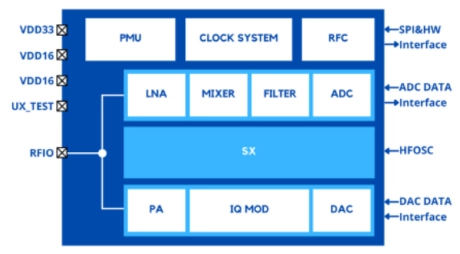

2.4GHz transceiver for Bluetooth application

- The GR1000 RF IPs are a 2.4GHz transcevier for Bluetooth application which have TX, RX, SX, and AFE blocks.

- T/R switch is integrated in our design. The IPs are fully compliant with the Bluetooth 5 standard.

- The transmitter output power can exceed 10dBm. The receiver current consumption is 12.6mA at maximum gain setting.

-

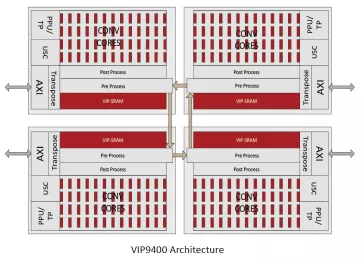

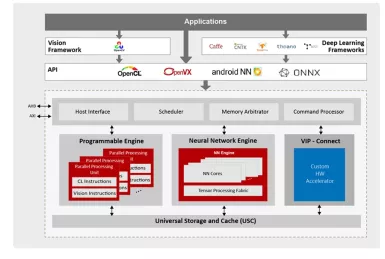

NPU IP for AI Vision and AI Voice

- 128-bit vector processing unit (shader + ext)

- OpenCL 3.0 shader instruction set

- Enhanced vision instruction set (EVIS)

- INT 8/16/32b, Float 16/32b

-

NPU IP for Data Center and Automotive

- 128-bit vector processing unit (shader + ext)

- OpenCL 1.2 shader instruction set

- Enhanced vision instruction set (EVIS)

- INT 8/16/32b, Float 16/32b in PPU

- Convolution layers