Viterbi decoder IP

Filter

Compare

35

IP

from

15

vendors

(1

-

10)

-

LTE Viterbi Decoder

- High performance in low SNR

- Low power design for HW implementation

- Minimum HW cost in ASIC implementation

- Flexible HW architecture

-

16-ACS Multi Function Viterbi Decoder

- 16, 32, 64 or 256 states (memory m = 4, 5, 6 or 8, constraint lengths 5, 6, 7 or 9) Viterbi decoder

- Up to 574 MHz internal clock

- Up to 95 Mbit/s for 16, 32, or 64 states or 31 Mbit/s with 256 states

- Rate 1/2, 1/3, 1/4 or 1/5 (inputs can be punctured for higher rates)

-

Viterbi Decoder

- Supports 1/N coderates

- Configurable constraint length

- Configurable generator polynomials

- Configurable precision of state metrics

-

16 State DVB-S2/DVB-S2X Tail Biting Viterbi Decoder

- 16 state (memory m = 4, constraint length 5) tail biting Viterbi decoder

- Rate 1/5 (inputs can be punctured for higher rates)

-

LTE / WiFi Viterbi decoder

- Scalable throughput/area level, selectable prior Core synthesis (3 levels)

- High throughput reachable(1-2 Gbps)

-

Viterbi Decoder

- Parameterizable Viterbi decoder

- Available for ispXPGA and ORCA 4

- Single clock synchronous design

- Soft decision with parameterizable soft width

-

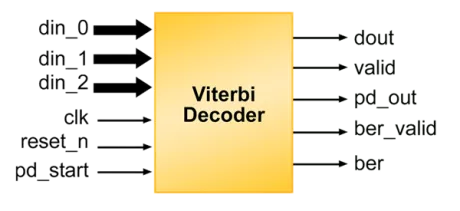

Viterbi Decoder

- Fully synchronous design

- Fully synthesizable

- Optimized for high performance and low resources

- Low implementation loss

-

Multi Function Viterbi Decoder

- 16, 32, 64 or 256 states (memory m = 4, 5, 6 or 8, constraint lengths 5, 6, 7 or 9) Viterbi decoder

- Up to 331 MHz internal clock

-

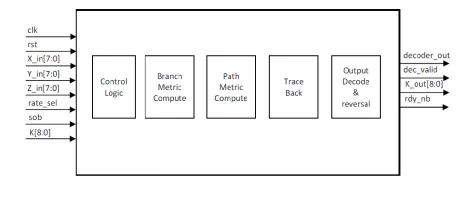

WCDMA Release 9 compliant Viterbi Decoder

- 3GPP TS 25.212 V 9.5.0 Release 9

- Supports all block sizes i.e., K=40 - 504.

- Constraint length of 9

-

1024 State 3GPP2 Viterbi Decoder

- Up to 258 MHz internal clock

- Up to 14.4 Mbit/s

- Rate 2/3, 1/2, 1/3 or 1/4