VITA IP

Filter

Compare

17

IP

from

14

vendors

(1

-

10)

-

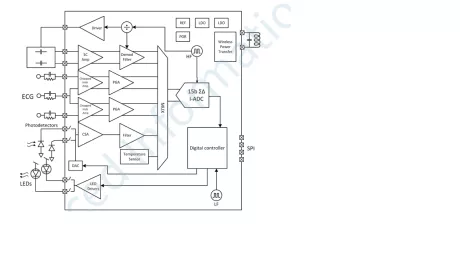

Vital signs healthcare sensor interface

- Two Channels of multi-lead electrocardiogram (ECG)

- Temperature sensor

- Differential capacitive sensor channel

-

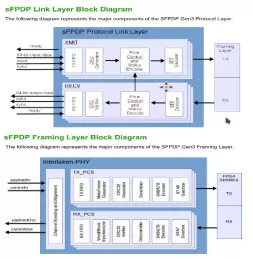

Serial Front Panel Data Port Gen3

- VITA 17.3-2018 Compliant

- Multi-lane channel bonding support

- 64B/67B Framing Layer

-

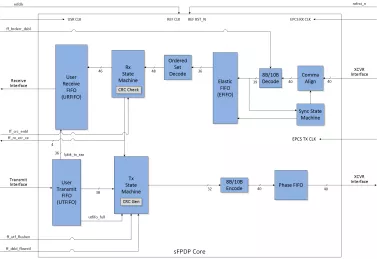

Serial Front Panel Data Port (sFPDP) IP Core

- Supports 1/2/2.5/10 Gigabit sFPDP rates

- Adheres to VITA 17.1-2015

- Complete hardware-based protocol offload

- High performance full-bandwidth operation

-

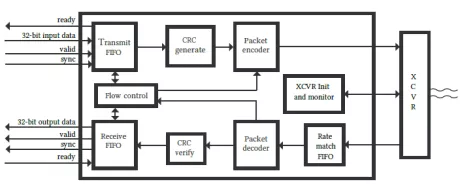

Serial FPDP

- VITA 17.1-2003 Compliant

- Conforms to FC-PH disparity rules

- Multi-lane channel bonding wrapper

- Independent data / system clock domains

-

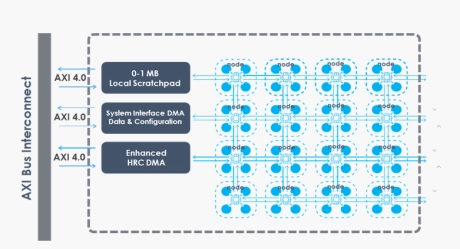

Neuromorphic Processor IP (Second Generation)

- Supports 8-, 4-, and 1-bit weights and activations

- Programmable Activation Functions

- Skip Connections

- Support for Spatio-Temporal and Temporal Event-Based Neural Network

-

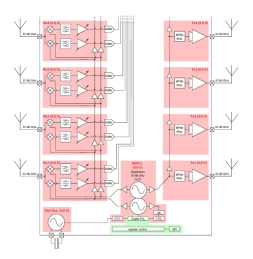

Ultra-low-power 60 GHz radar-on-chip

- CSEM has developed a low-cost, ultra-low-power 60 GHz MIMO FMCW PHY that can be integrated into radar-on-chips with custom digital processing for specific applications.

- This solution leverages CSEM’s decades of experience in ultra-low-power RF CMOS system-on-chip design.

-

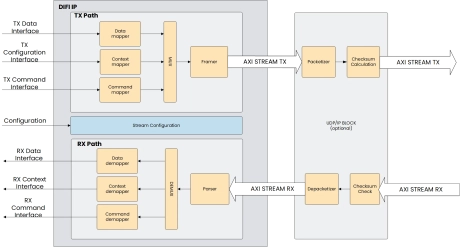

DiFi IP core

- The DiFi IP core is a highly scalable and silicon agnostic implementation of the IEEE-ISTO Std 4900-2021: Digital IF Interoperability Standard v1.2.1 targeting ASIC, and FPGA technologies.

- The DiFi implementation builds on long-time experience designing IP cores for sending and receiving Radio IQ data over Ethernet networks, and delivers a flexible engine that is prepared for tight integration with software applications.

-

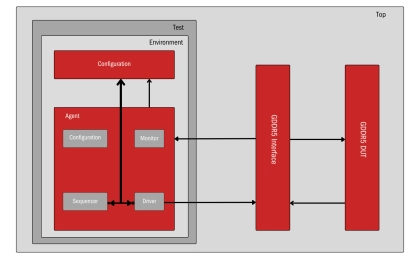

GDDR5 Controller - Verifies memory compliance, boosts performance, and ensures reliability

- The GDDR5 Memory Controller Verification IP (VIP) is a robust solution designed to verify the compliance and performance of GDDR5 memory controllers. It ensures adherence to GDDR5 specifications, enabling high-speed data transfers, low latency, and power efficiency for advanced systems.

- This VIP is vital for applications requiring high data throughput and low latency, such as GPUs, gaming consoles, VR systems, HPC, AI accelerators, and data centers. It ensures reliable, high-performance memory operations across a variety of demanding use cases

-

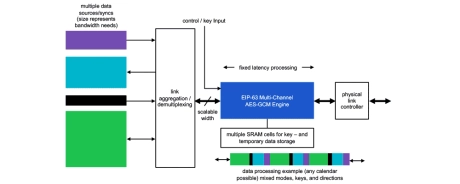

Inline cipher engine for PCIe, CXL, NVMe, 5G FlexE link integrity and data encryption (IDE) using AES GCM mode

- The ICE-IP-63 (EIP-63) is a scalable high-performance, multi-channel cryptographic engine that offers AES-GCM operations as well as AES-CTR and GMAC on bulk data.

- Its flexible data path is suitable to scale from 100 Gbps to 2.4 Tbps to provide a tailored engine with minimal area for your application.

- The FIFO-like data interface makes it possible to perform frame processing for many different protocols, including MACsec, IPsec, and OTN security.

-

Power Switch

- High Efficiency: Optimizes power usage by controlling the supply to different system components as needed

- Low On-Resistance: Ensures minimal voltage drop and power loss when the switch is active

- Fast Switching Time: Provides rapid transition between on and off states, crucial for responsive power management

- Integrated Protection: Includes features like over-current, over-voltage, and thermal protection to ensure safe operation