UltraScale IP

Filter

Compare

110

IP

from

28

vendors

(1

-

10)

-

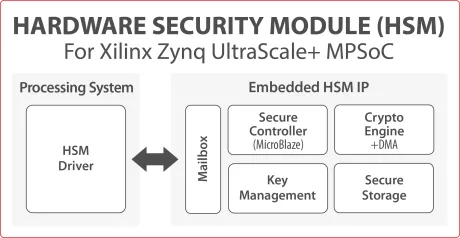

Hardware Security Module (HSM) for Xilinx Zynq UltraScale+ MPSoC platform

- The HSM IP module is a Hardware Security Module for a wide range of applications.

- It is developed, validated and licensed by Secure-IC (partner of Xilinx) as an FPGA-based IP solution dedicated to the Xilinx Zynq UltraScale+ MPSoC platform.

-

Zynq UltraScale+ RFSoC RF Data Converter

- Up to 16 14-bit 6.554 GSPS RF-DACs

- Eight 12-bit 4.096 GSPS RF-ADCs, or 16 12-bit 2.058 GSPS RF-ADCs, depending on the device

- Supports phase alignment between multiple converters channels on a single or multiple devices

- Pre-programs RF-DAC and RF-ADC with key user-defined parameters

-

Zynq UltraScale+ MPSoC Processing System IP

- Enable/Disable I/O Peripherals (IOP)

- Enable/Disable AXI I/O ports (AIO)

- MIO Configuration

- Extended MULTIPLE USE I/Os (EMIO)

-

UltraScale+ Device Integrated Block for PCI Express (PCIe)

- Designed to PCI Express Base Specification 3.1

- PCI Express Endpoint, Legacy Endpoint or Root Port Port Modes

- x1, x2, x4, x8 or x16 link widths

- Gen1, Gen2 and Gen3 link speeds

-

UltraScale Integrated 100G Ethernet Subsystem

- Supports 10 lanes x10.3125 CAUI-10, 4 lanes x25.78125G CAUI-4 or dynamically switchable CAUI-4 and CAUI-10 mode

- No charge 100G Ethernet MAC and PCS license key enabled

- Optional fee based soft 100G RS-FEC for UltraScale FPGAs

- 1588 1-step and 2-step hardware time stamping

-

UltraScale / UltraScale+ Interlaken

- The lane logic only mode allows each serial transceiver to be used to build a fully featured Interlaken interface. In devices with 48 serial transceivers, up to 600 Gb/s of total throughput can be sustained.

- The protocol logic supported in each integrated IP core scales up to 150 Gb/s. The Interlaken integrated IP core solution is designed to be compliant with Interlaken Protocol Definition, Revision 1.2, October 7, 2008.

- The integrated IP core implements both the lane logic and protocol logic portions of the specification, which saves approximately 60k+ System Logic Cells per instantiation and uses about 1/8th the power of equivalent soft implementations.

-

UltraScale Interlaken

- The lane logic only mode allows each serial transceiver to be used to build a fully featured Interlaken interface. In devices with 48 serial transceivers, up to 600 Gb/s of total throughput can be sustained.

- The protocol logic supported in each integrated IP core scales up to 150 Gb/s. The Interlaken integrated IP core solution is designed to be compliant with Interlaken Protocol Definition, Revision 1.2, October 7, 2008.

- The integrated IP core implements both the lane logic and protocol logic portions of the specification, which saves approximately 60k+ System Logic Cells per instantiation and uses about 1/8th the power of equivalent soft implementations.

-

UltraScale Integrated 100G Ethernet MAC/PCS

- Supports 10 lanes x10.3125 CAUI-10, 4 lanes x25.78125G CAUI-4 or dynamically switchable CAUI-4 and CAUI-10 mode

- No charge license key enabled

- 1588 1-step and 2-step hardware time stamping

- Allows insertion of custom logic such as RS-FEC between the 100G Ethernet integrated block and GT

-

UltraScale Gen3 Integrated Block for PCI Express (PCIe)

- High Peformance and High Bandwidth Applications

- Compute and Data Co-processing Applications

- Medical Imaging, High-Performance Computing & Communications Packet Processing