USB 2.0 PHY Device Controller IP

Filter

Compare

193

IP

from

18

vendors

(1

-

10)

-

USB 2.0 Device Controller version 4 with Active Clock Gating to save active power

- Configuration options to maximize performance and minimize CPU interrupts

- Flexible parameters enable easy integration into low and high-latency systems

- Transfer- or transaction-based processing of USB data based on system requirements

- Configurable data buffering options to fine-tune performance/ area trade-offs

-

AXI USB 2.0 Device Controller

- AXI-4 based host Interface. AXI-4 Lite for Slave Interface and optional AXI-4 Master interface for DMA mode

- Supports High Speed and Full Speed USB 2.0 specification

- Supports high speed, high bandwidth isochronous transactions

- Supports up to eight endpoints, including one control endpoint 0. Endpoints 1 to 7 can be bulk, interrupt, or isochronous and are individually configurable

-

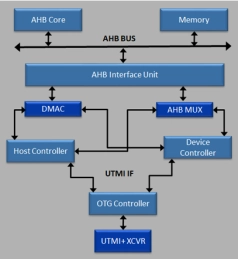

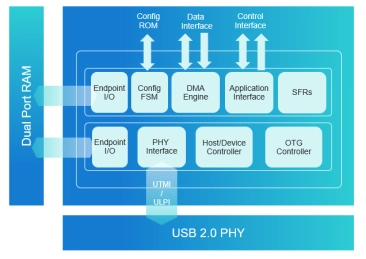

USB 2.0 OTG Dual Role Device (DRD) Controller

- Compliant with OTG Supplement Rev. 1.0a

- USB 2.0 Compliant

- Supports 480 Mbit/s (HS), 12 Mbit/s (FS), and 1.5 Mbit/s (LS)

- Supports Session Request Protocol (SRP) and Host Negotiation Protocol (HNP)

-

USB 2.0 Hi-Speed OTG Controller Subsystem w/AHB Interface Supporting HSIC (config. as Device only or Full Speed only)

- Configuration options to maximize performance and minimize CPU interrupts

- Flexible parameters enable easy integration into low and high-latency systems

- Transfer- or transaction-based processing of USB data based on system requirements

- Configurable data buffering options to fine-tune performance/ area trade-offs

-

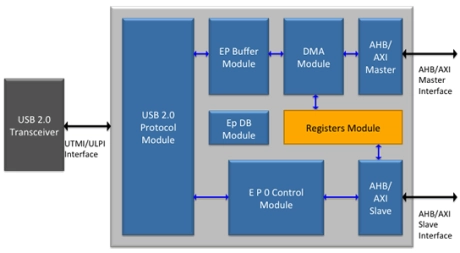

USB 2.0 Device IP Core

- High speed support: 480 Mbit/s

- Full speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI/ULPI interface

-

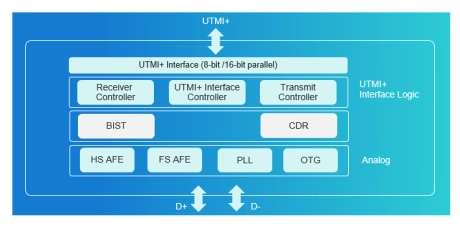

USB 2.0 PHY

- Designed to the USB 2.0 specification, and operates at High Speed (480Mbps), Full Speed (12Mbps), and Low Speed (1.5Mbps)

- Complies with the UTMI v1.05 specification

- Multiple reference clock supported from 9.6MHz up to 52MHz

- 8-bit 60MHz and 16-bit 30MHz parallel interfaces

- Battery Charging Specification v1.2

-

AXI 2.0 USB Device IP

- AXI4-Lite standard user interface. Connects as a 32-bit slave on AXI interface

- USB serial interface engine implemented to support USB2.0 full speed and high speed interface

- Supports ULPI interface to external PHY chip

- Supports control, bulk, interrupt and isochronous transfers on USB interface

-

USB 2.0 Controller

- Support for Link Power Management (L0 through L3)

- Scatter-gather DMA with Arm® AMBA® AXI interface

- Up to 8 IN and 8 OUT configurable endpoints

- Supports Attach Detection Protocol

-

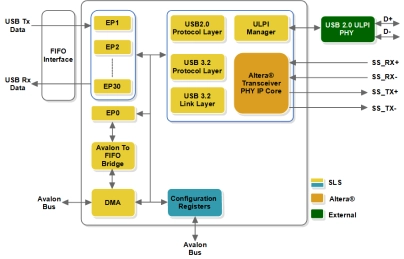

USB 20Gbps Device Controller

- Leveraging the benefits of USB 10Gbps and 5Gbps device controller, USB 20Gbps is designed using the FPGA built-in transceiver.

- It is a one-stop solution for all USB requirements ranging from USB 3.2 to USB 2.0.

- It supports SuperSpeed+ (SSP x2/x1), SuperSpeed (SS), High Speed (HS) and Full Speed (FS) communication modes.

-

USB 2.0 Digital Controller IP

- Fully supports Hi-Speed (480 Mbps), Full Speed (12 Mbps), and Low Speed (1.5 Mbps) (USB 2.0 Speeds) specifications

- Configurable root hub supports 1 to 15 downstream ports

- 60MHz or 30MHz input clock, and 48MHz and 12MHz input clocks

- ULPI and UTMI+ interfaces for rapid PHY integration