USB 2.0 IP

Filter

Compare

491

IP

from

48

vendors

(1

-

10)

-

USB 2.0 HS PHY Interface

- The USB PHY IP is UTMI interface compatible and a dedicated circuit for full-function USB 2.0 transceivers.

- It is a mixed-signal circuit, with the analog part including the transmitting and receiving circuits, level conversion circuits, bus driver circuits, etc., and the digital part including the transmitting and receiving and speed switching control circuits, encoding and decoding circuits, serial-to-parallel and parallel-to-serial conversion circuits, as well as digital CDR circuits, etc.

-

USB 2.0 PHY

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version 1.0

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- USB Data Recovery and Clock Recovery on receiving

- SYNC and EOP generation on transmit packets and detection on receive packets

-

USB 2.0 Mass Storage Devices Design Platform

- The USB 2.0 Mass Storage Design Platform is a complete, integrated solution, dedicated to a wide range of USB-based Mass Storage Devices.

- You can use it in various applications, like portable flash memory, digital audio player, card reader or digital camera.

-

USB 2.0 Human Interface Devices Design Platform

- The USB 2.0 HID Design Platform is a complete, integrated solution, dedicated to a wide range of USB-based Human Interface Devices, like mouse, keyboard, and tablet.

-

USB 2.0 Audio Devices Design Platform

- The USB 2.0 Audio Design Platform is a complete, integrated solution, dedicated to USB-based Audio Devices, like microphones and speakers.

-

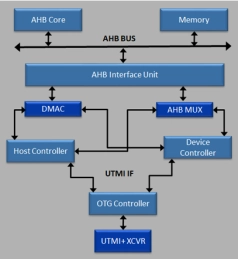

USB 2.0 OTG Dual Role Device (DRD) Controller

- Compliant with OTG Supplement Rev. 1.0a

- USB 2.0 Compliant

- Supports 480 Mbit/s (HS), 12 Mbit/s (FS), and 1.5 Mbit/s (LS)

- Supports Session Request Protocol (SRP) and Host Negotiation Protocol (HNP)

-

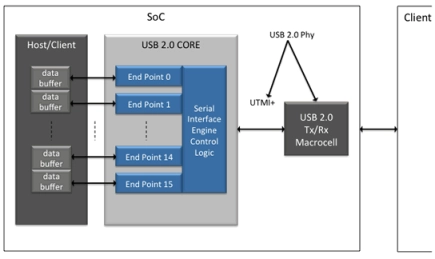

USB 2.0 PHY IP core

- Complies with USB specifications, rev. 2.0 and 1.1

- Complies with UTMI+ specification, level 3, rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

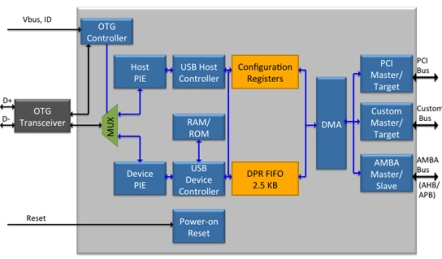

USB 2.0 OTG IP Core

- High speed support: 480 Mbit/s

- Full speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI/ULPI interface

-

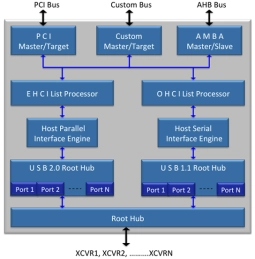

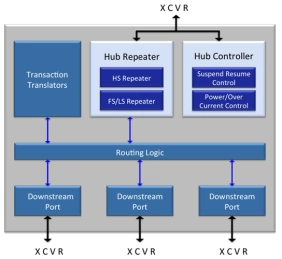

USB 2.0 Hub IP Core

- The USB 2.0 Hub IP core is a USB 2.0 specification compliant hub core that supports 480 Mbit/s in High Speed (HS) mode, 12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS) mode.

- The USB 2.0 Hub IP core consists of the Hub Controller, Hub Repeater, Transaction Translators, Routing Logic, and Downstream Ports.

-

USB 2.0 Host IP Core

- The USB 2.0 Host IP is a USB 2.0 specification compliant host IP core with an optional AHB, PCI, or custom host interface.

- The USB 2.0 Host IP supports 480 Mbit/s in High Speed (HS) mode. 12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS) mode.