UDP IP Hardware Stack UDP IP Off-Load Engine IP

Filter

Compare

10

IP

from

5

vendors

(1

-

10)

-

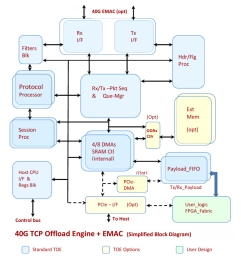

40G-1K Sess. TCP + UDP Offload Engine

- Highly customizable hardware IP block. Easily portable to ASIC flow, Xilinx/Altera FPGAs or Structured/ASIC flow.

- Eighth Generation TOE and System Solutions provide ‘Ultra-Low Latency’ and Ultra-High Performance with highest TCP bandwidth in Full Duplex. Network Tested and mature TCP protocol offload implementation

- All stages of Full TCP stack implemented in High performance hardware

-

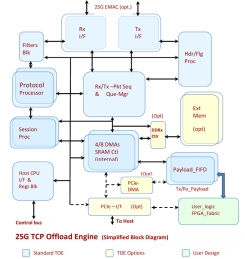

25G-1K Sess. TCP + UDP Offload Engine

- Highly customizable hardware IP block. Easily portable to ASIC flow, Xilinx/Altera

- FPGAs or Structured/ASIC flow.

- Eighth Generation TOE and System Solutions provide ‘Ultra-Low Latency’ and Ultra-High Performance with highest TCP bandwidth in Full Duplex. Network Tested and mature TCP protocol offload implementation

- All stages of Full TCP stack implemented in High performance hardware

-

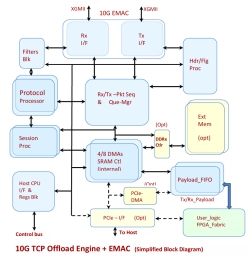

10G-16K Sess. TCP + UDP Offload engine (INT-20011-16K)

- Highly customizable hardware IP block. Easily portable to ASIC flow, Xilinx/Altera FPGAs or Structured/ASIC flow.

- Seventh Generation TOE and System Solutions provide ‘Ultra-Low Latency’ and Ultra-High Performance with highest TCP bandwidth in Full Duplex. Network Tested and mature TCP protocol offload implementation

- All stages of Full TCP stack implemented in High performance hardware

-

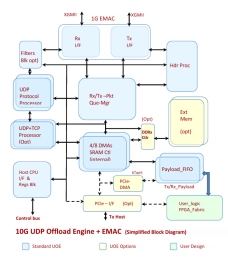

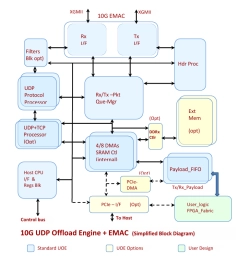

10G UDP Offload Engine UOE+MAC+PCIe+Host_IF Ultra-Low Latency (SXUOE+PCIe)

- Highly customizable hardware IP Core. Easily portable to ASIC flow, Xilinx/Altera

- FPGAs or Structured/ASIC flow.

- Provides Ultra-Low latency and highest bandwidth (NETWORK PROVEN)

-

10G UDP Offload Engine UOE+MAC+Host_IF Ultra-Low Latency (SXUOE)

- INT 15011 is the only SOC IP Core that implements a full 10G bit UDP Stack in Handcrafted, Ultra-High Performance, Innovative, Flexible and Scalable architecture which can also be easily customized for end product differentiation.

- It provides the lowest latency and highest performance in the industry, No exceptions…..

-

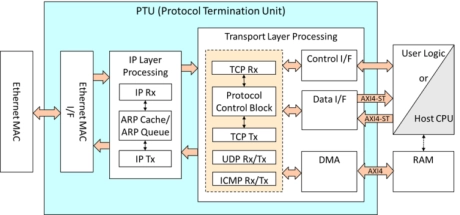

TCP/UDP Offload Engine

- Full hardware TCP/UDP protocol stack realize both high performance and guaranteed delivery

- The TCP/UDP offload engine supports simultaneous connection of more than 10,000 sessions on a single core, which is a feature of our IP along with its high quality and performance.

-

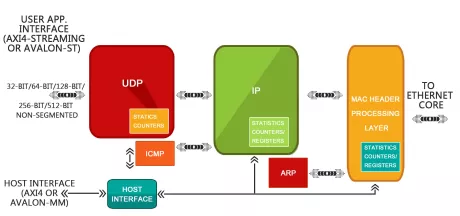

UDP/IP Offload Engine (UOE)

- Implements RFC 768 for UDP.

- Implements RFC 791 for IPv4.

- Implements RFC 2460 for IPv6.

-

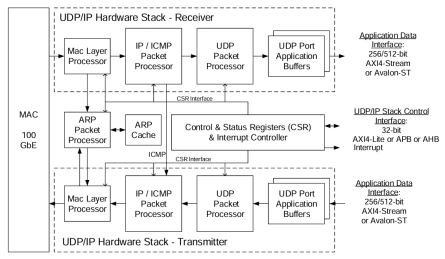

UDP/IP – 100 GbE Protocol Hardware Stack

- 100 GbE network links

- Low latency, high-performance wire-line performance

- Internet Protocol (IP) Packet Processor: IP & ICMP (Internet Control Message Protocol) Protocol; Host IP address filter, IP header checksum check & generator, userselectable Maximum Transmission Unit (MTU), Unicast & MulticastPacket support; Compliance with IETF IPv4/IPv6 RFCs

- User Datagram Protocol (UDP) Packet Processor: Support for up to 256 UDP Ports; UDP header checksum check & generator; Compliance with IETF UDP RFCs

-

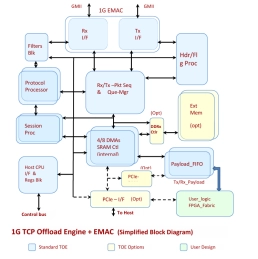

1G TCP Offload Engine TOE Very Low Latency (TOE)

- Ideal for high performance and mid performance specialized, differentiable ASICs or FPGAs for Network security or Network infrastructure applications

- Less than 4000 Xilinx slices, Altera ALMs or 150,000 ASIC gates + on-chip memory

- Fully integrated 100 M bit/1-G bit high performance EMAC.

- Scalable MAC Rx FIFOs and Tx FIFOs make it ideal for optimizing system performance.

-

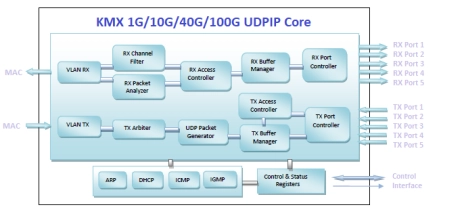

100G UDP/IP Hardware Protocol Stack Core

- The core Implements a UDP/IP hardware protocol stack that enables high-speed communication over a LAN or a point-to-point connection.

- It is ideal to offload systems from demanding tasks of UDP/IP and to enable media streaming in both FPGA and RISC designs.

- The core supports ARP request, reply and manages 32-entry ARP cache. ICMP ping reply is included.