Synopsys IP

Filter

Compare

1,973

IP

from

19

vendors

(1

-

10)

-

HPC MACsec Security Modules for Ethernet

- IEEE 802.1ae, IEEE 802.1br Support

- 100 Gbps—1.6 Tbps

- Can reach higher throughputs scalable to 3.2 Tbps

- Supports also lower performance modes down to 10 Gbps

-

ASIL B / ISO 26262 and ISO 21434 Compliant 1G-25G MACsec Security Module

- Synopsys MACsec Security Modules use scalable AES-GCM cryptography to provide confidentiality, integrity, authentication, and replay protection for Ethernet traffic.

- These modules integrate seamlessly with Synopsys Ethernet MAC & PCS IP, supporting high data rates with low latency. By incorporating Synopsys MACsec Security Modules into Ethernet IP solutions, networking SoC designers can ensure end-to-end security for data in motion between Ethernet-connected devices.

-

UALinkSec Security Module

- UALink 200 v1.0 / UALinkSec specification support

- Plug and play with Synopsys UALink controller

- Supports 200 GT/s per lane, enabled by silicon-proven Synopsys 224G PHY IP

- Support bifurcation of up to 4 ports

-

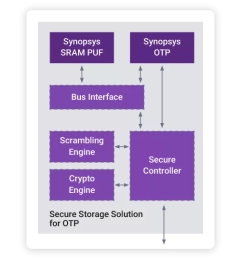

Secure Storage Solution for OTP IP

- Advanced Security: Encrypted storage in OTP using dynamic root key from SRAM PUF

- System-Level Security Extension: Add-on allows sharing the SRAM PUF to protect chip-level assets

- Flexible Security Configuration: Secure regions within OTP can be tailored to meet specific needs

-

Verification IP for AMBA AXI4-Stream

- Native SystemVerilog/Verilog with UVM

- Runs natively on all major simulators

- Reference Verification Platform

- Built-in verification plan and coverage

-

Verification IP for AMBA ATB

- Trace Data Transfer (Valid, ready signaling)

- Narrow Trace Data Transfer (Data Valid Bytes signaling)

- Flow Control (Valid, ready signaling)

- Flush Request Response (Flush Valid, Ready signaling with Data transfer)

-

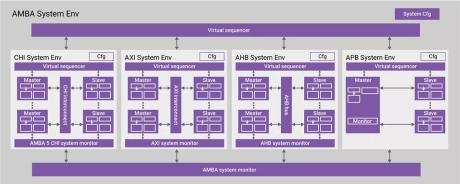

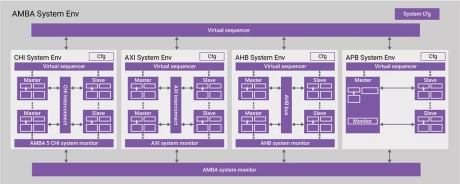

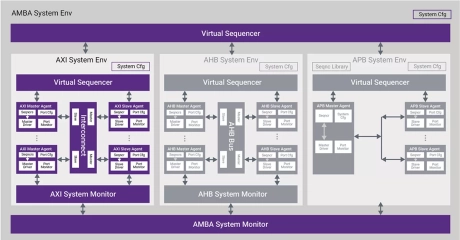

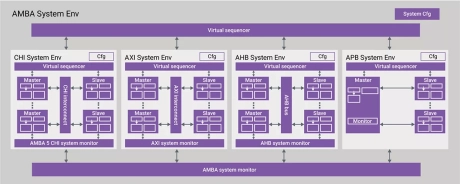

Verification IP for AMBA AXI

- Complete protocol support for AXI5, AXI-J/K, AXI4, AXI4-Lite, AXI3

- Programmable number of Managers, Subordinates, and Port Monitors

- Interconnect model

- System Monitor

-

Verification IP for Arm AMBA CHI Protocol

- AMBA 5 CHI-A/B/C/D/E/F/G

- Request node, secondary node agents and monitor

- Complete port-level checks

- Supports all interface types

-

Verification IP for AMBA APB

- Native SystemVerilog/Verilog with UVM

- Includes primary, secondary, monitor

- Runs natively on all major simulators

- Built-in UVM sequence library

-

Verification IP for AMBA AHB

- Complete protocol support for AHB5, AHB3, AHB2, AHB-Lite, and AHB Multi Layer

- Includes primary, secondary, monitor

- Configurable bus model

- Backdoor access to AHB secondary memory