Still Image Encoder IP

Filter

Compare

21

IP

from

9

vendors

(1

-

10)

-

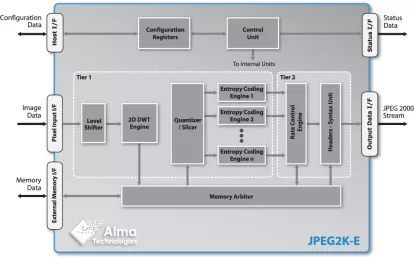

JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression

- ISO/IEC 15444-1 JPEG 2000 Image Coding System Compliance

- Programmable JPEG 2000 Encoding Options

- Smooth System Integration

-

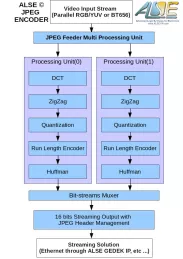

High-Speed JPEG Video Encoder

- Speed and Area-Optimized encoder engine suitable for both still image and real-time video compression.

- 8 bits (byte) Streaming output interface with Backpressure. Easy to connect to the ALSE Ethernet communication engine for example. Output format is 8x8 YUV Blocks (4:2:2).

- Supports any image resolution up to 64k x 64k.

- Suitable for still image and real-time video (streaming).

-

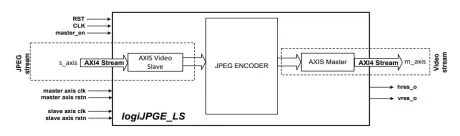

Lossless MJPEG Encoder

- Plug-and-Play IP core with Xilinx implementation tools (Vivado)

- Free reference designs available for AMD-Xilinx ZCU102 on request

-

JPEG Encoder 1-pixel/clock

- - Image Format: Frame sequential method

- - Input/Output Format: YUV 4:4:4/4:2:2/4:2:0/4:0:0

- - Data bus protcol: AXI

- - CPU bus protcol: AHB

-

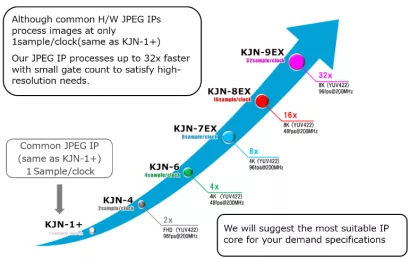

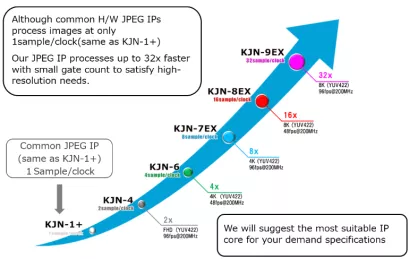

JPEG Encoder 8K (YUV422) 96fps@200MHz. (32Sample/clk)

- ?Based on JPEG Extended DCT-based process Standards.

- ?With proprietary algorithm, we offer fast, small scale and low power consumption core.

-

JPEG Encoder Full HD(YUV422) 30fps@126MHz(1Sample/clk)

- The arithmetic accuracy satisfies the requirement of compliance testing of JPEG Part2 (ISO/IEC10918-2).

- Image Data I/O Format:Block Interleaved Format.

- Image Size:Any size that can be divided by MCU unit.

- Operation mode like processing mode, image size, DRI value etc. are set in internal register via external CPU.

-

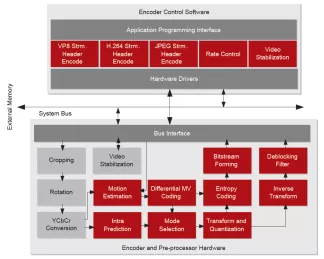

Multi-format video encoder IP Core

- Multi-format video encoder supporting H.264, VP8 and JPEG.

- First HW IP encoder to support VP8 for Google’s WebM and WebRTC.

- Designed for battery operated devices using state-of-the-art power saving methods leading to unbeatable power consumption.

-

H 265 Video Encoder IP

- All-hardware Design (without embedded processors)

- • High Speed (Low latency)

- • Small Silicon Footprint

- • Low Power

-

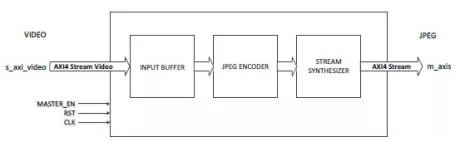

Motion JPEG Encoder

- Supports Xilinx® Zynq®-7000 AP SoC and 7 series FPGA families

- Compliant with the Baseline Sequential DCT mode of the ISO/IEC 10918-1 JPEG standard

-

JPEG Encoder FPGA Core

- JPEG Compliance (ISO/IEC 10918-1) High-accuracy and high-speed DCT core options Fixed entropy table, sixteen programmable quantization tables (8 Chroma, 8 Luna) Supports all possible scan configurations and all JPEG formats for input and output data (up to 8 color components) Any image size up to 16K x 16K 1 clock/pixel greyscale, 1.5 clock/pixel YUV 4:2:0, 2 clock/pixel YUV 4:2:2 Custom versions available