SAR ADC IP

Filter

Compare

207

IP

from

46

vendors

(1

-

10)

-

14-bit 12.5MSPS SAR ADC - Tower 65nm

- The A14B12p5M is a high-performance, low-power analog-to-digital converter (ADC) intellectual property (IP) block designed for applications requiring both high speed and power efficiency.

- It offers 14-bit resolution with maximum sampling rate of 12.5 megasamples per second (MS/s), making it ideal for RF communications, radar sensing, and aerospace and defense applications.

-

10-bit SAR ADC - XFAB XT018

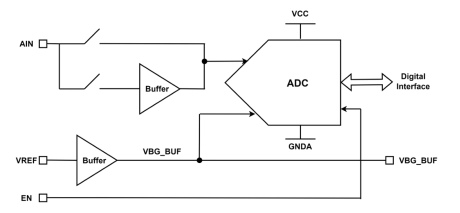

- The TS_ADC_10b_X8 is a 10-bit capacitive successive approximation register (SAR) Analog-to-Digital converter (ADC).

- It operates with a 3.3 V analog power supply, a 1.8 V digital power supply, and an external voltage reference.

- The ADC converts single-ended input voltages and requires no external S/H circuit.

-

Low-power 8-bit 80 MHz SAR ADC

- The data converter IP portfolio includes low-power SAR ADCs, flash ADCs, and high-speed I/Q DACs optimized for RF and baseband paths

- With resolutions from 3-bit to 12-bit and sampling rates up to 640 MHz, these converters combine small silicon area, excellent dynamic range, and low energy per conversion

- They are ideal for wireless transceivers, mixed-signal SoCs, sensor interfaces, and portable devices.

-

Low-power 8-bit 80 MHz SAR ADC

- The data converter IP portfolio includes low-power SAR ADCs, flash ADCs, and high-speed I/Q DACs optimized for RF and baseband paths

- With resolutions from 3-bit to 12-bit and sampling rates up to 640 MHz, these converters combine small silicon area, excellent dynamic range, and low energy per conversion

- They are ideal for wireless transceivers, mixed-signal SoCs, sensor interfaces, and portable devices.

-

12-bit, 400 MSPS SAR ADC - TSMC 12nm FFC

- 12-bit Resolution

- 400 MSPS Sampling Rate

- 1 GHz Input Bandwidth

- Differential voltage input

- 4.2 mW Power