RISC-V Multicore Vector Processor IP

Filter

Compare

23

IP

from

8

vendors

(1

-

10)

-

Multi-core capable RISC-V processor with vector extensions

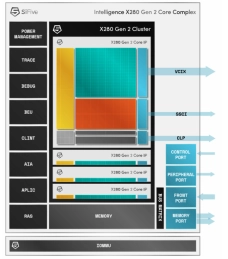

- The SiFive® Intelligence™ X280 Gen 2 is an 8-stage dual issue, in-order, superscalar design with wide vector processing (512 bit VLEN/256-bit DLEN).

- It supports RISC-V Vectors v1.0 (RVV 1.0) and SiFive Intelligence Extensions to accelerate critical AI/ML operations.

-

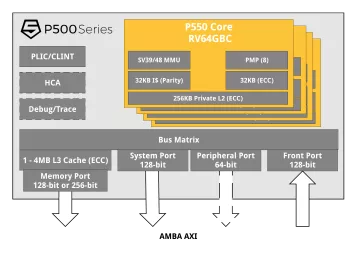

64-bit RISC-V Multicore Processor with 1024-bit Vector Extension

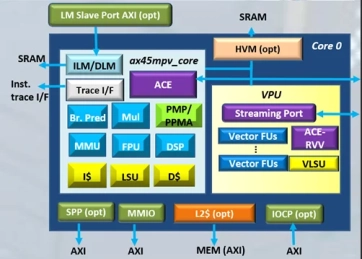

- 64-bit in-order dual-issue 8-stage CPU core with up to 1024-bit Vector Processing Unit (VPU)

- Symmetric multiprocessing up to 8 cores

-

High-performance 64-bit RISC-V architecture multi-core processor with AI vector acceleration engine

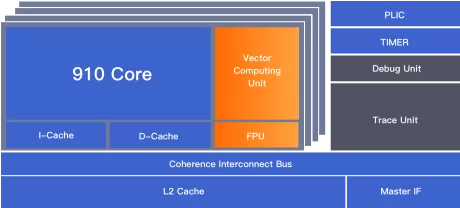

- Instruction set: RISC-V RV64GC/RV 64GCV;

- Multi-core: Isomorphic multi-core with 1 to 4 optional clusters. Each cluster can have 1 to 4 optional cores;

-

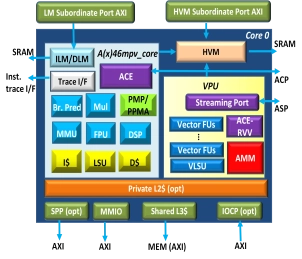

64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

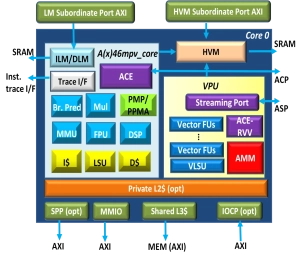

- 2 different packages with or without vector: AX46MPV, AX46MP

- in-order dual-issue 8-stage CPU core with up to 2048-bit VLEN

- Symmetric multiprocessing up to 16 cores

- Private Level-2 cache

- Shared L3 cache and coherence support

-

32 bit RISC-V Multicore Processor with 256-bit VLEN and AMM

- AndesCore™ A46MP(V) 32-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeStar™ V5 architecture and Andes Matrix Multiply (AMM) extension.

- It supports RISC-V standard “G (IMA-FD)”, “ZC” compression, “B” bit manipulation, DSP/SIMD ‘P’ (draft), “V” (vector), CMO (cache management) extensions, Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

Highly efficient out-of-order RISC-V vector application processor series

- Full support for the RVA22 RISC-V profile specification

- Best-in-class RISC-V performance efficiency

-

High performance three-issue, out-of-order RISC-V vector application processor

- Breakthrough RISC-V performance

- Enabling next generation applications

-

ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- High-speed, 32-bit, dual-issue, 10-stage pipeline

- Multicore support for up to 16 CPUs and up to 16 user hardware accelerators per processor cluster

-

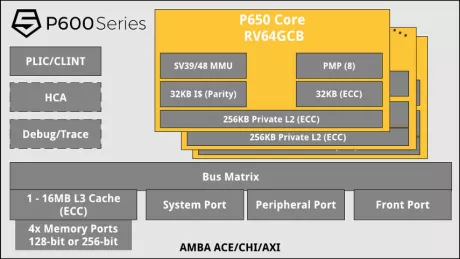

Highest performance four-issue, out-of-order RISC-V vector application processors

- Breakthrough RISC-V performance

- Multi-core, multi-cluster processor configurations with up to 16 cores

-

ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- High-speed, 32-bit, dual-issue, 10-stage pipeline

- Multicore support for up to 16 CPUs and up to 16 user hardware accelerators per processor cluster