RISC-V CPU IP

Filter

Compare

92

IP

from

28

vendors

(1

-

10)

-

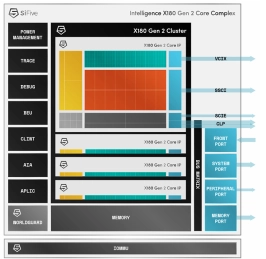

Multi-core capable 64-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X180 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 64-bit version, X100 series IP delivers higher performance and better integration with larger memory systems.

-

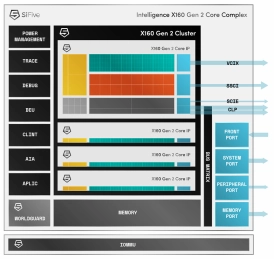

Multi-core capable 32-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X160 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 32-bit version, X100 series IP can be optimized for power efficiency and severely area-constrained applications.

-

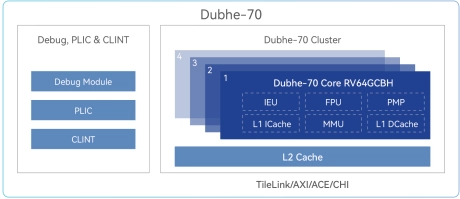

Ultra-low power consumption out-of-order commercial-grade 64-bit RISC-V CPU IP

- Dubhe-70 is a 9+ stage, 3-issue, out-of-order CPU IP that supports the rich RISC-V instruction set, RV64GCBH_Zicond_Zicbom_Zicboz_Zicbop.

- With a score of 7.2 SPECInt2006/GHz, Dubhe-70 targets applications that require highly energy-efficient computation, including mobile, desktop, AI, and automotive.

-

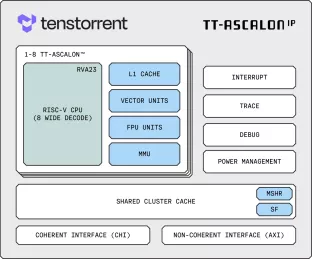

RISC-V CPU IP

- RISC-V RVA23 Compliant

- >18 SPECint2006/GHz

- 8-wide decode unit

- Advanced branch predictor

-

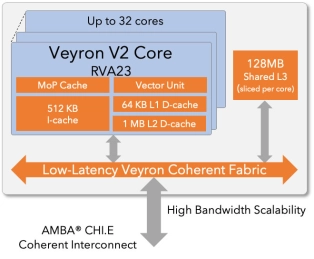

High-performance RISC-V CPU

- Fully compliant with the RVA23 RISC-V specification

- Comparable PPA to Arm Neoverse V3 / Cortex-X4

- Standard AMBA CHI.E coherent interface for SoC and chiplet integration

- Co-architected with Veyron E2 for seamless vector, AI acceleration, and big-little style heterogeneous compute configurations

-

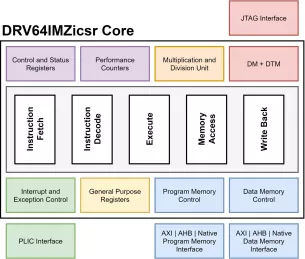

64-bit RISC-V CPU with M, Zicsr extensions and External Debug support

- Five-stage pipeline

- Harvard architecture

- RV64I Base RISC-V ISA

-

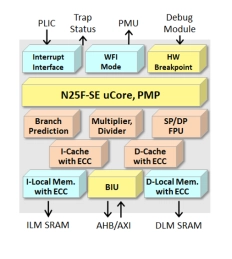

Low Power RISCV CPU IP

- RISC-V RV32 instruction set

- Machine mode only

- 32 vectorized interrupts

- Standard debug as defined per RISC-V

-

RISC-V CPU IP With ISO 26262 Automotive Functional Safety Compliant

- AndeStar™ V5 Instruction Set Architecture (ISA), compliant to RISC-V technology

- Floating point extensions

- Bit-manipulation extensions

-

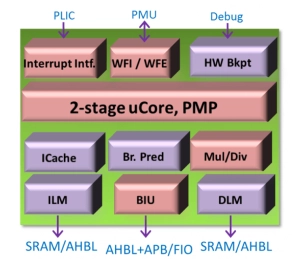

Ultra Compact 32-bit RISC-V CPU Core

- AndesCore™ N22 is a 32-bit 2-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications that require low energy consumption and small area.

- It is compliant to RISC-V technology with several efficient performance features, including simple dynamic branch prediction, instruction cache, and local memories.

-

RISC-V Processor - RV12 - 32/64 bit, Single Core CPU

- High Performance 32/64bit CPU

- Highly Parameterized

- Size and power optimized design

- Industry standard software support