Positioning IP

Filter

Compare

23

IP

from

14

vendors

(1

-

10)

-

L1 + L2 + L5 nine-channel positioning RX + SX

- The GNSS IP solutions support GPS, Glonass, Galileo, and Beidou constellations across L1, L2, and L5 bands

- Designed for low-power, high-sensitivity positioning, these receivers integrate fractional-N synthesizers, multi-band RF front-ends, and multi-channel tracking engines

- They enable robust acquisition and precision navigation for asset tracking, IoT devices, timing systems, and embedded mobility applications.

-

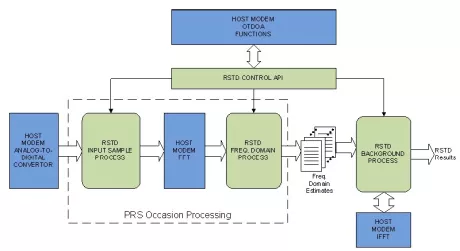

Signal processing IP core for LTE network assisted positioning and E911 indoor location accuracy standards

- 3GPP Rel. 9 through 13 compliant

- Optimized for commercial 16b DSP

- <140 MIPS during PRS occasion (6RB)

-

L5 GPS + Glonass + Galileo + Beidou receiver + fractional-N synthesizer

- The GNSS IP solutions support GPS, Glonass, Galileo, and Beidou constellations across L1, L2, and L5 bands

- Designed for low-power, high-sensitivity positioning, these receivers integrate fractional-N synthesizers, multi-band RF front-ends, and multi-channel tracking engines

- They enable robust acquisition and precision navigation for asset tracking, IoT devices, timing systems, and embedded mobility applications.

-

2-channel L1 + L2 + L5 GPS + Glonass + Galileo + Beidou receiver + fractional-N synthesizer

- The GNSS IP solutions support GPS, Glonass, Galileo, and Beidou constellations across L1, L2, and L5 bands

- Designed for low-power, high-sensitivity positioning, these receivers integrate fractional-N synthesizers, multi-band RF front-ends, and multi-channel tracking engines

- They enable robust acquisition and precision navigation for asset tracking, IoT devices, timing systems, and embedded mobility applications.

-

Advanced control timer

- 32-bit up, down, up/down auto-reload counter

- 32-bit programmable prescaler allowing dividing (also “on the fly”) the counter clock frequency either by any factor between 1 and 4294967296

-

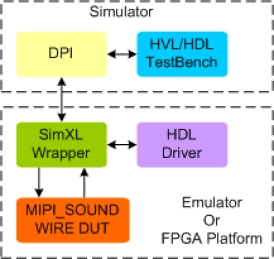

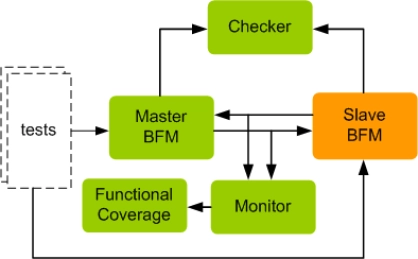

Verification IP for Soundwire

- A comprehensive VIP solution portfolio for Soundwire 1.0 used by SoC and IP designers to ensure comprehensive verification and protocol and timing compliance. Soundwire-Xactor implements a complete set of models, protocol checkers and compliance test suites in 100% native SystemVerilog and UVM.

-

-

MIPI SoundWire Verification IP

- Full MIPI SoundWire Master, slave and Monitor functionality

- Supports MIPI SoundWire version 1.2r08 Specifications

- Supports Basic PHY and High PHY mode

- Supports IO timing

-

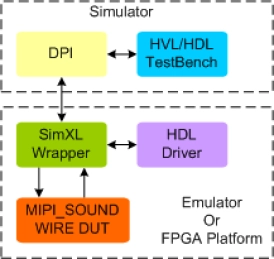

MIPI SOUNDWIRE Synthesizable Transactor

- Supports MIPI SoundWire version 1.2r08 Specifications

- Supports full MIPI SoundWire Master,Slave functionality

- Supports Basic PHY and High PHY mode

- Supports IO timing

-

MIPI SOUNDWIRE PSVIP

- Supports MIPI SoundWire version 1.2r08 Specifications

- Supports full MIPI SoundWire Master,Slave functionality

- Supports Basic PHY and High PHY mode

- Supports IO timing