PLL in 7nm IP

Filter

Compare

30

IP

from

6

vendors

(1

-

10)

-

M31 Digital PLL IP in 3nm, 5nm, 6nm, 7nm, 12nm, 16nm, 22nm,28nm,40nm

- Pure core voltage design

- Compact IP size (< 0.013mm²) and low power consumption (1.1mW @ 3GHz)

- Compatible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter (< ±15%/V)

-

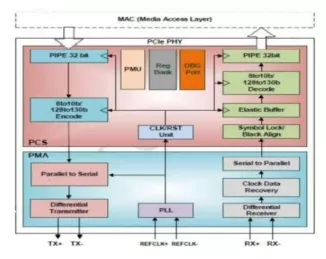

PCIe 3.0 Serdes PHY IP, Silicon Proven in TSMC 7nm

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

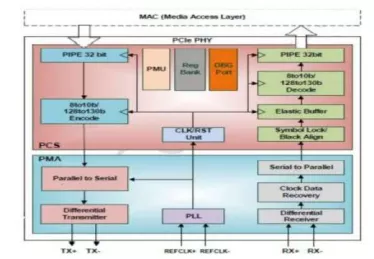

PCIe 4.0 Serdes PHY IP Silicon Proven in TSMC 7nm

- Compliant with PCIe 4.0 Base Specification

- Compliant with PIPE 4.4

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0 GT/s

- Supported physical lane width: x4

-

TSMC CLN7FFLVT 7nm Deskew PLL - 300MHz-1500MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

TSMC CLN7FFLVT 7nm Deskew PLL - 600MHz-3000MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

TSMC CLN7FFLVT 7nm Deskew PLL - 1200MHz-6000MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

TSMC CLN7FF 7nm Deskew PLL - 200MHz-1000MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

TSMC CLN7FF 7nm Deskew PLL - 400MHz-2000MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

TSMC CLN7FF 7nm Deskew PLL - 800MHz-4000MHz

- Designed to eliminate clock distribution latency in systems and individual chips.

- Precisely aligns the clock distribution output with a reference clock.

- Provides a zero-delay feedback divider and zero-skew divided clock outputs.

-

USB 2.0 PHY in TSMC(6nm, 7nm, 12nm, 16nm, 22nm, 28nm, 40nm, 55nm, 65nm, 90nm)

- Smallest USB 2.0 PHY IP worldwide (IP size of 55nm, 40nm, 28nm, and 16/12nm are less than 0.2mm2)

- Fully compliant with Universal Serial Bus (USB) 2.0 electrical specification

- Compliant with UTMI+ specifications (High-Speed, Full-Speed, and Low-Speed functions)

- Supports clock inputs from 10/12/19.2/24/25/27/30/40MHz crystal oscillator or external clock source