PLDA IP

Filter

Compare

2

IP

from

2

vendors

(1

-

2)

-

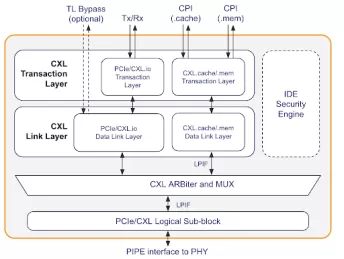

CXL 2.0 Controller

- Internal data path size automatically scales up or down (256, 512 bits) based on max. link speed and width for reduced gate count and optimal throughput

- Dynamically adjustable application layer frequency down to 8Mhz for increased power savings

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs (when supported)

-

PCIe Gen1/2 PHY

- Fully compliant with PCI-SIG’s PCIe v2.0 specification.

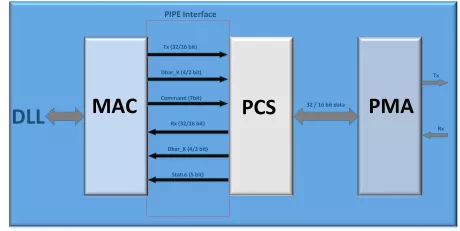

- PHY package includes configurable PIPE interface (8 bit/ 16 bit/ 32bit). User can choose the interface width as per the application requirement.

- Generates whole range of Ordered Sets as required by PCIe 2.0 Specification with synchronized LTSSM.

- IBM implementation compatible 8b/10b Encoder and Decoder.