PCI-Express IP

Filter

Compare

32

IP

from

12

vendors

(1

-

10)

-

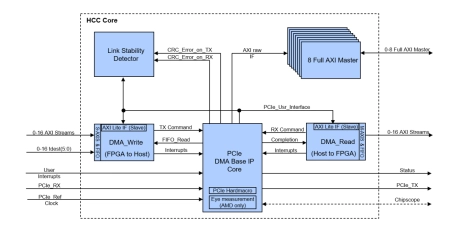

High Channel Count DMA IP Core for PCI-Express

- The High Channel Count (HCC) DMA IP core for PCI-Express is a powerful PCIe Endpoint with multiple industry standard AXI Interfaces.

- This IP addresses continuous streaming applications from up to 64 different data sources. Each channel is able to transmit data into a separate memory area.

- Up to 16 AXI Stream masters read DMA Data from the host and present it to the user logic. Additional 8 AXI4 masters are available to interface full AXI or AXI-Lite peripherals with the host.

-

Configurable PCI Express 4.0 Link Controller

- Compliant with "PCI Express™ Base Specification, Rev. 4.0 Version 1.0"

- Compliant with "PHY Interface For the PCI Express, SATA, and USB3.1 Architectures"

-

PCIe Controller

- Compliant to PCI Express base specification 5.0 (32 Gbps per lane) and backward compatible with PCI Express versions 4.0, 3.1, 2.0 and 1.1

- Supports configurable number of PFs and VFs for SR-IOV

- Architected for high link utilization and low latency

- Efficient receive and transmit-retry buffering scheme

-

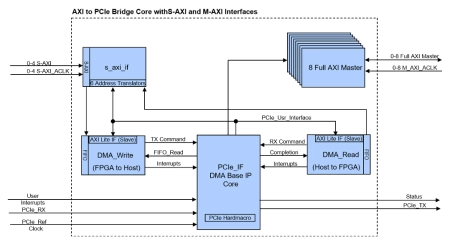

AXI Bridge for PCIe IP Core

- The AXI Bridge for PCIe IP core is the IP solution with a powerful mix of multiple industry standard memory mapped AXI Interfaces.

- The AXI Bridge IP core translates the AXI4 memory read or writes to PCI-Express Transaction Layer Packets and translates PCIe memory read and write requests to AXI4 transactions.

- All interfaces support fully parallel operation without any interferences. Interfaces that are not required can be turned off individually and do not occupy logic resources.

-

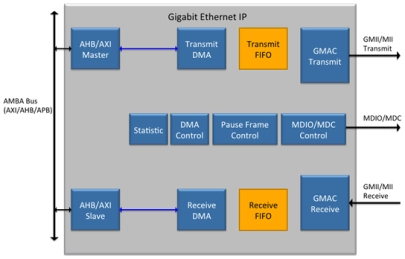

Gigabit Ethernet MAC IP Core

- The silicon-proven Gigabit Ethernet IP core provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

- It also supports optional Reduced MII (RGMII), and Serial GMII (SGMII).

-

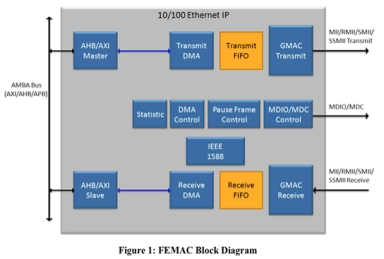

Fast Ethernet Media Access Controller

- The Fast Ethernet Media Access Controller (FEMAC) with AHB or AXI Interface core incorporates the essential protocol requirements for operation of 10/100 Mbps Ethernet/IEEE 802.3-2008 compliant node, and provides interface between the AHB or AXI Interface and the Media Independent Interface (MII) for the Ethernet operation.

- Optionally the core supports RMII (Reduced MII Interface) and SMII (Serial MII Interface) for reducing the pin count to interface with external PHY device.

-

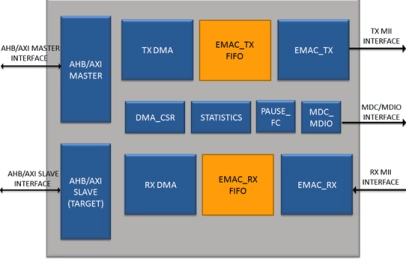

10/100 Ethernet MAC IP core

- The 10/100 Ethernet Media Access Controller (MAC) IP core is compliant with the Ethernet IEEE 802.3-2002 standard and has passed interoperability testing at UNH-IOL.

- The 10/100 Ethernet IP core provides an 10/100 Mbps Media Independent Interface (MII) and an optional processor interface; it also supports Reduced MII (RMII) and Serial MII (SMII).

-

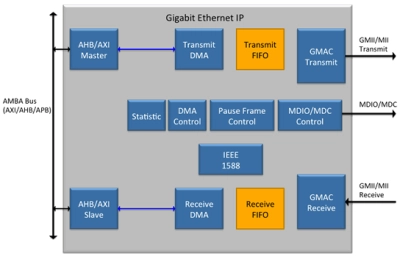

Gigabit Ethernet with IEEE 1588 and AVB

- The Gigabit Ethernet Media Access Controller IP is compliant with the Ethernet IEEE 802.3-2008 standard and supports protocol extensions for Audio Video Bridging (AVB).

- The Gigabit Ethernet IP provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

-

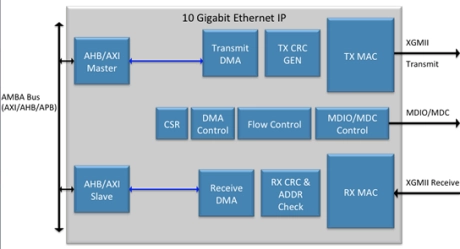

10 Gigabit Ethernet MAC IP Core

- The 10 Gigabit Ethernet (XGMAC) IP core is compliant with the Ethernet IEEE 802.3-2008 standard and provides an interface between AHB/AXI Bus and the 10 Gigabit Media Independent Interface (XGMII) using a powerful 64-bit Scatter Gather DMA.

- The 10 Gigabit Ethernet IP core is designed for applications such as integrated networking devices, host bus adapters, PCI-Express Ethernet controllers, and Ethernet adapter cards.