New Wave Design IP

Filter

Compare

15

IP

from

3

vendors

(1

-

10)

-

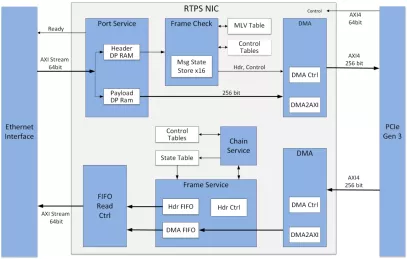

Ethernet Real-Time Publish-Subscribe (RTPS) IP Core

- OMG DDSI-RTPS 2.2 compliant interface with hardware-based offload

- Hardware DMA engines with message label mapped buffers

- Message label validation and filtering

- Host processor offloaded from all networking responsibilities

-

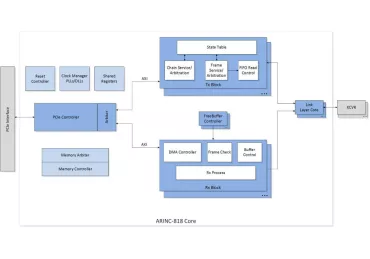

ARINC 818 Streaming IP Core

- Flexible video pixel bus input with synchronization signals (video_active, vsync, hsync) that supports a wide range of pixel depths and number of parallel pixels

- Compatible with all FC line rates up to 10G (incl. non-standard rates)

- Core handles synchronization and clock crossing into the FC clock domain. User clock can be asynchronous to the FC clock

- Automatic creation and maintenance of the Object 0 and container header

-

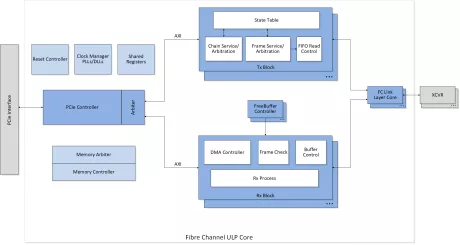

FC Upper Layer Protocol (ULP) IP Core

- FC-AE-RDMA & FC-AV compliant interface with hardware-based offload

- Hardware DMA engines map sequence data to host memory buffers

-

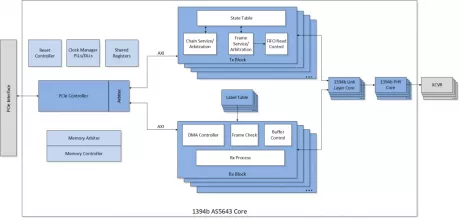

Mil1394 AS5643 Link Layer Controller IP Core

- AS5643 compliant interface with hardware based STOF offload

- Hardware DMA engines with message label mapped buffers

- STOF transmitter and receiver hardware functions

- Supports S100/S200/S400 data rates

-

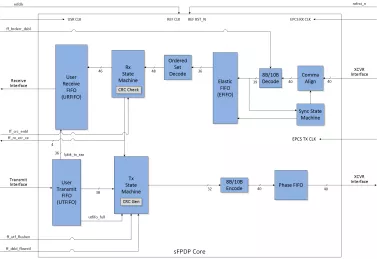

Serial Front Panel Data Port (sFPDP) IP Core

- Supports 1/2/2.5/10 Gigabit sFPDP rates

- Adheres to VITA 17.1-2015

- Complete hardware-based protocol offload

- High performance full-bandwidth operation

-

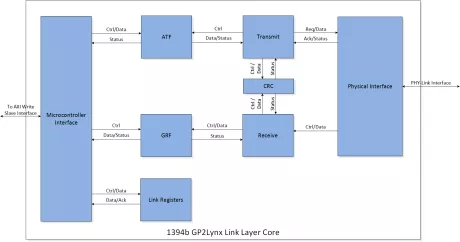

Mil1394 GP2Lynx Link Layer Controller IP Core

- AS5643 compliant interface with hardware-based STOF offload

- Supports S100/S200/S400 data rates

- Configurable number of GP2Lynx nodes in a single FPGA

- Legacy microprocessor or AXI host interface available

-

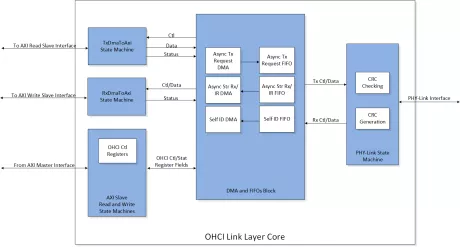

Mil1394 OHCI Link Layer Controller IP Core

- AS5643 compliant interface with hardware based STOF offload

- Supports S100/S200/S400/S800/S1600/S3200 data rates

- Configurable number of OHCI nodes in a single FPGA

- AXI-based host interface for embedded or PCIe based processors

-

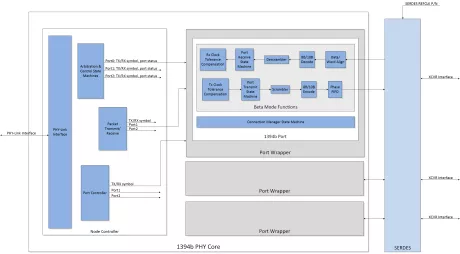

1394b PHY IP Core

- AS5643 compliant interface

- Supports S100 / S200 / S400 / S800 / S1600 / S3200 data rates

- Complete PHY layer implementation

-

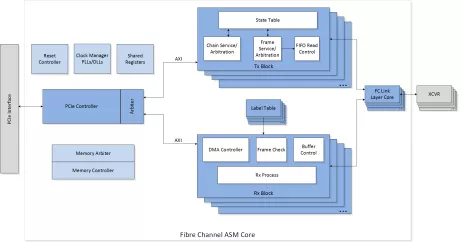

Fibre Channel ASM (Anonymous Subscriber Messaging) Core

- Message label validation checks performed in hardware

- Multiple user modes for receiving messages, including strictly mapped message-to-buffer and free-buffer implementations

- Transmit message chaining options provided

- Complete set of registers for managing core and configuring core options

-

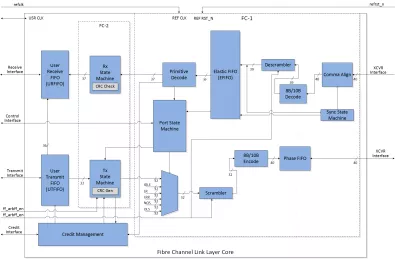

Fibre Channel Link Layer Core

- Complete FC1-FC2 functionality

- Intuitive streaming user interface

- Scales for multiple port designs