Netspeed IP

Filter

Compare

331

IP

from

13

vendors

(1

-

10)

-

Hyper-Bandwidth Multichannel Memory Subsystem

- Hyper-Bandwidth Multi-Channel - The fastest, most observable LPDDR3 subsystem you can drop into an SoC

- Supports an aggressive bandwidth envelope for LPDDR3, JEDEC-2133Mbps and up to 3200 Mbps on select process nodes.

- Includes hard QoS enforcement, traffic shaping, performance observability & self-tuning PHY front-end.

-

HBM4 PHY IP

- Supports JEDEC HBM4 DRAMs

- Supports data rates up to 12 Gbps

- Supports up to 32 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 64 32-bit pseudo-channels with 2048-bit PHY

-

DDR4/LPDDR4 PHY Interface

- The DDR PHY IP is a combination of hard macro, I/O Pad and synthesizable RTL to provide a physical interface to JEDEC standard DDR3/DDR4 SDRAM memories.

- The synthesizable RTL (ddr_phy_top) provides control functions such as initialization, SDRAM interface training, impedance calibration and programmable configuration controls.

-

MRDIMM DDR5 & DDR5/4 PHY & Controller

- The DDR IP Mixed-Signal MRDIMM DDR5 PHY and DDR5/4 Combo PHY provide turnkey physical interface solutions for ICs requiring access to JEDEC compatible SDRAM or MRDIMM/ RDIMM/ LRDIMM/ UDIMM DDR5 devices

- It is optimized for low-power and high-speed applications with robust timing and small silicon area

- It supports all JEDEC DDR5/4 SDRAM components in the market

-

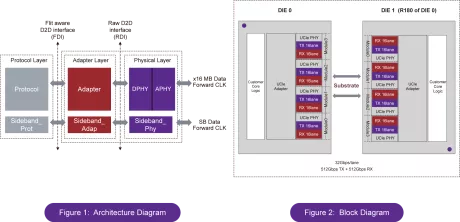

D2D UCIe 1.1

- Compatible with UCIe v1.1 specification

- Features single-ended, source-synchronous, and DDR I/O signaling

- Supports 32-bit (16-bits TX + 16-bit RX) data bus per module for standard packages

- Offers a high clock frequency up to 16GHz

-

PCIe 2.0 PHY, UMC 40LP, x1

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, UMC 40LP x4, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, UMC 40LP x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, UMC 28HPC+ x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, UMC 28HPC+ x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island